# DIGITAL COMPUTER REPORTER

A franchiste of their speciations of the same of the s

OFFICE OF NAVAL RESEARCH . MATHEMATICAL SCIENCES DIVISION

Vol. 12, No. 2

Gordon D. Goldstein, Editor Jean S. Campbell, Asst. Editor

April 1960

## TABLE OF CONTENTS

| COMPUT   | ERS AND DATA PROCESSORS, NORTH AMERICA                                                 | Page No |

|----------|----------------------------------------------------------------------------------------|---------|

| 1.       | Ballistic Research Laboratories, Computing Laboratory,                                 |         |

|          | New Computer, Aberdeen Proving Ground, Maryland                                        |         |

| 2.       | Bendix Computer Div. of Bendix Aviation, G-20, Los Angeles, Calif.                     | 1       |

| 3.       | University of Chicago, Institute for Computer Research, Maniac III,                    | 1       |

|          | Chicago, Illinois                                                                      | 6       |

| 4.       | Control Data Corp., 160 Computer and 180 Data Collector,                               | •       |

|          | Minneapolis, Minnesota                                                                 | 7       |

| 5.       | Los Alamos Scientific Laboratory, Maniac II, Los Alamos,<br>New Mexico                 | ,       |

| 4        |                                                                                        | 9       |

| 0.       | The Rice Institute, Computer Project, Houston, Texas                                   | 9       |

| 7.       | Stromberg Div., General Time Corporation, Transactor System,<br>Thomaston, Connecticut |         |

| 9        |                                                                                        | 10      |

| ٠.       | U. S. Naval Training Device Center, UDOFTT, Port Washington,<br>N. Y.                  | 11      |

| СОМРИТІ  | NG CENTERS                                                                             |         |

|          | Air Force Missile Development Center, Analysis and Computation                         |         |

| ••       | Division, Holloman Air Force Base, New Mexico                                          |         |

| 2        | AFC Computing and April 124 th                                                         | 11      |

|          | AEC Computing and Applied Mathematics Center, New York                                 |         |

| 2        | University, New York, N. Y.                                                            | 11      |

|          | U. S. Naval Missile Center, Pacific Missile Range, Point Mugu, California              | 12      |

| 4.       | U. S. Naval Weapons Laboratory, Computation Center, Dahlgren,                          |         |

|          | Virginia Virginia                                                                      | 12      |

| COMPUTE  | ERS AND CENTERS, OVERSEAS                                                              |         |

| 1.       | Standard Elektrik Lorenz AG, ER 56, Stuttgart, Germany                                 | 13      |

| MISCELLA |                                                                                        |         |

|          | Contribution for Digital Computer Newsletter                                           |         |

|          |                                                                                        | 14      |

Reproduced by the CLEARINGHOUSE for Federal Scientific & Technical Information Springfield Va. 2215!

Approved by

The Under Secretary of the Navy

20 August 1957

The document has retor public release and sale; its distribution is unlimited

NAVEXOS P-645

16

#### COMPUTERS AND DATA PROCESSORS, NORTH AMERICA

NEW COMPUTER-BALLISTIC RESEARCH LABORATORIES, COMPUTING LABORATORY-ADERDEEN PROVING GROUND, MARYLAND

A new general purpose electronic digital computer is being developed by the Computing Laboratory. The system will be used primarily for the solution of the scientific problems of ballistics research. Design emphasis has been placed on speed and ease of coding.

Arithmetic and Logical Unit. The arithmetic and logical unit will be capable of performing arithmetic and logical operations in both fixed and floating point binary notation. Addition will be at the rate of two 68-bit words per microsecond. Planned instructions are: add, subtract, multiply, divide, extract, compare, shift, accumulate, and boolean type instructions.

Memory System. The system consists of a 4096 seventy-two bit word (68 plus 4 parity bits) high-speed magnetic core memory—capable of being expanded to 16,384 words, a magnetic drum, and a magnetic tape handling system. The memory cycle time will be 2 microseconds or less. Drums and tapes will comprise an auxiliary memory.

Control Unit. A control unit with 63 index registers will perform indexing operations concurrently with arithmetic and logical operations. Since the control unit will select and decode instructions prior to use, the average time required for the execution of a complete instruction will be about 6 microseconds. Sixty-eight bits of an instruction word are used to specify the type of arithmetic or logical operation, any three of 63 index registers, and any three of 16,384 words of high-speed main memory. The numeric words consist of 64-bits, a sign, and a 3-bit tag. The binary point lies between the fourth and fifth bits of the 64-bit number. For floating point numbers, the numeric word consists of a 3-bit tag, a sign bit, a 56-bit coefficient, and an 8-bit exponent. The exponent is a power of 16. Since the 63 index registers may be addressed as regular memory cells, any instruction may operate upon the index addresses as well as the main memory. The cycle time for the index memory will be 1 microsecond. In addition, allowance is made for up to 8, 192 words of 1 microsecond fixed memory for the storage of subroutines frequently used by the programmers. A single program instruction will initiate a complete subroutine automatically. Thus, no time is lost to read in, modify, store, and shuttle subroutines around whenever main memory space is needed.

Input-Output. The input-output equipment consists of magnetic tape stations, punched cards, high-speed printer, and manual and visual devices. For maximum efficiency and versatility in information handling, off-line conversion equipment will include tape-to-card, card-to-tape, tape-to-printer, and card-to-printer devices. The input-output units are controlled through five trunks and buffers, permitting concurrent operation of the card reader, card punch, a magnetic drum system, and two magnetic tape trunks, which are capable of controlling 16 tape stations. Rapid transfers to and from main memory allow the arithmetic and logical unit to have memory access during input-output operations. Thus, input-output operations may occur simultaneously with arithmetic computations and logical operations. A special circuit determines which of the input-output trunks has priority on memory access for the brief time required to fill or empty the buffer of the input-output device.

Code Checking. Code checking features will include stopping on any selected address, the display of the contents of any memory cell, the display of normal or abnormal conditions, the ability to manually store in any selected memory cell, and the ability to transfer control to any part of the system. Confidence in results is obtained through parity checking.

### G-20 - BENDIX COMPUTER DIV. OF BENDIX AVIATION - LOS ANGELES, CALIF.

The new Bendix G-20 system is composed of a high-speed central processor, a control buffer, and matched input-output units including magnetic tape, high-speed printer, and punched card and punched tape equipment. These elements operate in a common language

and are interconnected by a communication system which permits their operation in a wide variety of on-line and off-line systems.

For a small system the central processor may operate a number of accessory devices directly. Such a system permits the high speed of the central processor to be used at modest cost for engineering and scientific problems requiring minimum input and output. It is also an effective system for a modest data processing task, in which case much of the time of the processor might be used in the detailed controlling and operation of accessory units.

To meet larger requirements the system may be expanded by adding memory to the central processor, by adding more direct computer communication lines, and through the addition of control buffer units. Such a group represents a medium scale system in which only an operators console and high-speed control buffer and magnetic tape units are operated directly by the central processor. For larger scale systems the processor may be equipped with additional communication lines. These lines afford direct simultaneous communication with the processor's memory. The control buffer units, which are small stored program computer-like devices, are each directed by the computer to perform a sequence of operations which they can perform with little or no computer assistance, leaving the computer free for other tasks. When a control buffer unit, with its associated sub-system, has completed its assignment or encountered a problem beyond its capability, it may interrupt the central processor, informing it of the status of that part of the operation which it has performed. This interrupt system, along with the real-time clock provided, permits it to manage a system including a number of control buffer operated sub-systems efficiently.

In addition to on-line operation as described, the control buffer may operate as the center of a variety of off-line systems. In the on-line and off-line systems the same printer, punched card and tape, and magnetic tape equipment are used.

The system is well suited as a scientific computing, data processing, or business computing system. It has excellent facilities for automatic compilation of programs from algebraic and business oriented languages. In the paragraphs which follow the various system elements are described in some detail.

Central Processor. The G-20 is a high-speed single-address computer with magnetic core storage and parallel arithmetic. Operations are performed in extended precision floating-point octal to 14 digits. Two forms of floating-point storage are available: single precision, equivalent to half the precision of the arithmetic unit, and using one word; or entended precision, the full precision of the arithmetic unit, using two words. A fixed-point mode of operation is available using storage of 9 octal digits. Sixty-three conventional index registers are available and the command structure permits addressing of almost unlimited flexibility. Thirty-two of the commands can be repeated automatically any desired number of times on a sequence of operands. Input-output simultaneous with computation is available.

The basic central processor contains about 5,000 transistors and 30,000 diodes in addition to one or two modules of core memory containing 4,096 words each. (Additional core memory is in a separate cabinet.) Components are fixed to printed circuit cards mounted on strips. The strips are arranged on hinged panels which swing out to make all parts of the unit easily accessible. The equipment is 66" wide, 28" deep, and 64" high, and weighs 2,000 pounds. With a 4,096 word memory it requires 2.5 KVA of 115 or 230 volt, single phase, 60 cycle power. Other voltages or frequencies are available on special order.

The minimum core storage supplied for the system consists of 4,096 words of 32 bits each. Up to 7 additional 4,096 word modules may be added to the basic system to provide a total core memory of 32,768 words, with each word directly addressable.

Addressing Facilities. The G-20 provides for flexible addressing and indexing without disturbing the contents of the accumulator. A string of numbers and/or addresses is built up in a register known as the operand assembly register. This string can be used as an operand, or an address, or as the address of the first term of a new string. The process can be continued indefinitely. This makes possible operands of the forms:

```

A + B + ... + (I) + (J) + ...

(A + B + ... + (I) + (J) + ...)

(A + B + ... + (I) + (J) + ...) + D + E + ... + (K) + (L) + ...

((A + B + ... + (I) + (J) + ...) + D + E + ... + (K) + (L) + ...)

where A, B, etc. are based addresses

J, etc. are index addresses

= contents of

```

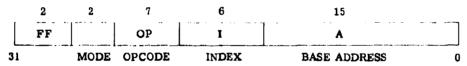

The way in which this is accomplished is explained in more detail in the following paragraphs. A command word (See Table 1) carries, in addition to the operation code and flag bits, a 2-bit mode code and two addresses: a base address A of 15 bits and an index address I of 6 bits. The mode bits specify the way in which A and I are to be interpreted to form an operand or an operand address. The information can be summarized as shown in Table 2 which indicates the manner in which the operand X is formed from the previous contents, if any, of the operand assembly register, combined with the two addresses.

Table 1. Command Word

Table 2. Addressing modes

In the simple case where one word is used for a command the initial contents of OA will be zero. For this case the operand, X, for each of the four modes (0 through 3) will be:

0

$$A + (I) - - \rightarrow X$$

1  $(A) + (I) - - \rightarrow X$

2  $(A + (I)) - - \rightarrow X$

3  $((A) + (I)) - - \rightarrow X$

It can be seen that mode 2 represents the conventional indexed operand address where A is the base address and I one of the 63 index registers. For problems requiring a greater number of indexes, any number of words can be combined in one command using as indexes any number of locations situated anywhere in core memory. This flexibility is made possible through the use of "preparation" Op codes, which perform address computation, leaving the computed address standing in the operand assembly register as indicated by (OA) in Table 2. The symbolic assembly routine provided with the equipment selects the number and variety of command words to perform the required addressing. Thus, a command requiring three indexes is written:

$$CA \qquad A + (I) + (J) + (K)$$

which might mean clear and add the term  $\boldsymbol{A}_{ijk}$  of a three dimensional array.

Operation Codes. The operation codes include arithmetic operations, arithmetic tests, logic operations, logic tests, as well as store, register, index, and transfer control commands. There are also address preparation commands and input-output commands. A

repeat command applicable to add/subtract operations, arithmetic tests, logic operations, and logic tests permits a command to be repeated any number of times on a sequence of operands.

In general, arithmetic commands are automatically carried out in extended precision floating-point (14 octal mantissa plus 2 octal exponent) in the arithmetic unit. The distinction between extended precision and single precision exists only in store commands.

Logic operations are carried out to 32-bit precision and the other bits of the accumulator are cleared. Arithmetic and logic test commands leave the accumulator undisturbed.

Arithmetic. The G-20 performs all arithmetic in integer floating-point octal. Numbers have the form of a positive or negative octal integer multiplied by a positive or negative integral power of 8. Hardware representation is 3 binary digits for each octal digit of the number. The command structure makes available automatic adjustment of the exponent to a pre-assigned value, or to zero, to facilitate operations in fixed point or in integers.

The arithmetic unit performs all arithmetic to 14 octals precision and the numbers can be so stored. It is also possible to store automatically the most significant 7 octals, a fixed exponent number of 9 octals, an integer of 9 octals, or an integer of 7 octals.

The maximum range of numbers handled without scaling is:

$$\pm$$

8-63 to  $\pm$  8<sup>77</sup> to  $\pm$  10<sup>-57</sup> to  $\pm$  10<sup>69</sup>

approximately. In single precision the upper limit is  $\pm 8^{70}$  or about  $\pm 10^{63}$ . A non-biasing round-off rule is applied automatically except in division and "integer" operations, where truncation is used instead.

Operating Speeds. Average times in microseconds for representative operations are:

|   | One-Word Precision |                   | Extended Precision |                   |

|---|--------------------|-------------------|--------------------|-------------------|

|   | Fixed<br>Point     | Floating<br>Point | Fixed<br>Point     | Floating<br>Point |

| + | 7                  | 13                | 13                 | 13                |

| - | 8                  | 13                | 13                 | 13                |

| x | 49                 | 49                | 62                 | 62                |

| + | 98                 | 98                | 78                 | 78                |

Accessory Equipment. The accessory units which may be attached to the system include the control buffers, control consoles, paper tape stations, magnetic tape units, card and printer couplers, line printers, and core memory modules.

Control Buffer. The control buffer is a stored program computer-like unit employing a 1,024 character magnetic core memory. This memory is used as a store for commands as well as a buffer for input-output data. It connects to two communication lines; the computer line and a buffer line. In operation it communicates briefly with the computer or magnetic tape equipment at high speed on the computer line, and then operates the slower input-output equipment on its buffer line.

The buffer can execute complex programs including conditional transfers of control based on its own state, interrupt requests it has received, and specific querries it has made of associated units. It receives and transmits blocks of information and translates character codes at high speed. It receives and transmits interrupt signals which can be used to interlock a multi-element system in the performance of a complex operation.

A representative control buffer operation might be as follows: The G-20 transmits instructions over its communication line to the buffer. The control buffer then begins executing the instructions which cause it to switch from the computer communication line to the buffer

communication line. It then instructs the card reader to read several cards, transmitting the information to the communication line. The buffer receives and stores the information from the cards. It may then translate the punch card codes to a code specified by the central processor, after which it stores the information in a block on magnetic tape. After repeating this sequence of operations until all cards have been read, the buffer then transmits an interrupt request directly to the central processor indicating completion of the assigned task.

As an example of off-line control buffer operation, consider the case of a buffer, a magnetic tape unit, and a printer at a location remote from the central processor. In this case, output tapes prepared by the processor are transported to the remote location. The initial blocks of information written on the tape may contain instructions to the control buffer for listing the data written on other blocks of the tape, permitting an essentially automatic remote printing operation.

Control Console. The control console provides the operator with the facilities necessary to initiate and control the execution of programs. The control console has three important functions: 1) To permit, when required, manual control of the system via a typewriter. 2) To provide a typed record of all manual console operations. 3) To type messages, under program control, to the operator.

The typewriter keyboard is equipped with 88 characters which provide for the typing of upper and lower case letters, digits, and 26 special characters.

Paper Tape Station. The Bendix paper tape station PT-10 provides punching at 100 characters per second and reading at 500 characters per second for standard 8-hole paper tape.

Magnetic Tape System. Any number of tape units may be connected to a computer line or buffer line. Information is recorded on the tape in blocks formed from characters of 8bits plus parity. One word is, therefore, recorded as four 8-bit characters. The data transfer rate for reading and writing on tape is 60,000 8-bit characters per second. Individual tape units can move the tape forward or backward a specified number of blocks while off-line. It is recommended, but not required, that magnetic tapes be connected to the computer line whether the system contains buffers or not. This gives complete flexibility in the use of magnetic tapes and permits access to any tape by the G-20 or any control buffer. The fraction of computer primary line time occupied by transfer of information to and from magnetic tapes is not the limitation in most practical systems. Although the tape can operate with blocks of arbitrary length, to facilitate continuous addressing, information on magnetic tapes is stored in blocks of fixed length. Any block can be written over. The standard block length for which service routines are provided is 512 words or 2,048 characters. If the recommended system is used, each word in tape library is uniquely addressable and the beginning address of each block is written on the tape at the beginning of the block. The programmer need only specify the tape address he desires and the supervisory routine keeps track of which physical tape handler contains the tape reel in question.

Card and Printer Coupler. The card and printer coupler is used to control line printers and 80-column card machines. The coupler, when used to drive an output device, receives information serially by characters and delivers information in parallel to all of the columns of the output device. It is also able to perform the inverse operation.

Once an input-output function has been initiated, the card and printer coupler controls subsequent transmissions until an entire card has been read or punched or a complete line has been printed. The card coupler is capable of reading and punching cards in three formats. An extended Hollerith code of 256 different characters includes as a subset all of the code configurations which can be produced by a keypunch or read by a tabulator. Row binary and a column binary modes are also available for processing cards using other character representations or for compact information storage.

When operating a high-speed printer, the coupler is capable of either fixed cycle or so-called free wheeling cycle operation. In this mode the printing process begins at the completion of any paper feed cycle without waiting for the character roll to return to a fixed index.

Line Printers. G-20 printers provide for line-at-a-time printing of numeric or alphanumeric data at rates of from 600 to 1250 lines per minute with up to 120 characters per line. A continuously revolving print roll carries a number of complete sets of printing characters, each set occupying one circumferential track on the print roll. A line of print is created by driving the paper and ribbon against the print roll by means of a set of individually timed hammers, one for each print column. Timing of each hammer determines the character to be printed in that column. The paper remains stationary during printing and is upspaced after a complete line has been printed. The print cycle can begin at any character position and need not begin at the same character for succeeding lines. The standard character set uses a 63-character alphabet.

Communication System. The Bendix Digital Communication System is an approach toward organizing all of the components of a complex system on a common language basis. The common language understood by all units is a language of 10-bit characters which, in general, mean the same to all units. The first 8 of the 10 bits are coded command or data information. These 8 bits correspond to one character in the buffer, one typewriter character, one character on magnetic tape, one character on paper tape, or one character in the G-20. The 8 bits can also represent in card operations one extended Hollerith character, the upper or lower half of a card column (with 2 leading zeros) in column binary, or 8 successive positions in row binary. Inside the G-20, four characters are combined to form a word, but the decomposition and recombination of characters are combined to form a word, but the decomposition and recombination of characters to G-20 words is automatic. The 9th and 10th bits are data flag and odd parity respectively. The maximum distance permitted between units in the G-20 communication system is 1,000 feet, dictated by transmission characteristics of the lines.

#### MANJAC III - UNIVERSITY OF CHICAGO, INSTITUTE FOR COMPUTER RESEARCH-CHICAGO, ILLINOIS

The activities of the Institute are currently concerned with the design and construction of the Maniac III computer, and with the development of utility programs for it. Maniac III is intended not only to provide a means for requirements of the University, but also to provide a means for studying computer systems.

The instruction set has been formed by systematically combining basic operations in a way that gives versatility without undue complexity. The set is divided into eight classes. This subdivision leads to engineering as well as conceptual convenience. Specifically, the classes are: Floating Point Arithmetic, Specified Point Arithmetic, Supplementary Arithmetic, Formal Manipulation, Index Computation, Data Transmission, Auxiliary System Operations, and Miscellaneous Operations.

A single form of number representation is used for the three arithmetic classes; the 48-bit word is split into an 8-bit exponent part and a 40-bit coefficient part. Complement representation is used for negative numbers.

Floating Point Arithmetic in Maniac III differs from the procedure so designated in most computers, in that coefficient parts are handled in unnormalized form, according to a system which is intended to afford an estimation of the precision of results. Specified Point Arithmetic is a generalization of what is usually referred to as "fixed point" operation, which affords arbitrary but controlled positioning of the radical point. The use of a single representation eliminates any need for distinguishing between "fixed point numbers" and "floating point numbers." Supplementary Arithmetic operations provide means for shifting coefficients, so that numbers can be scaled or adjusted to new exponents; for independently manipulating signs or exponents of numbers; and for converting exponent and index representations to standard arithmetic form. This class includes a group of instructions designed to operate on coefficients as segments of longer representations, to facilitate multi-precision calculation. A square root instruction is also available.

The Formal Manipulation class of instructions is used for operating on words in a non-arithmetic way. Three types of "shift" and two types of "extract," supplemented by a "formal add," permit the common variety of internal "data processing" to be carried out efficiently.

The Index Computation class contains a group of instructions for setting and altering the contents of eight index registers, and for conditional jumps in the normal instruction sequence.

The Data Transmission class is used to copy words from one location or register to another. Incorporated in these orders is an "indirect addressing" feature. Some instructions for altering and storing contents of the indicator register are also included in this class.

The Auxiliary System instructions are used in connection with the transfer of information between the central computer and the auxiliary equipment. The computer can continue executing instructions while these relatively slow devices are in action, and then respond to an interrupt signal when they have finished.

The Miscellaneous Operation class contains instructions for certain simple types of number adjustment, and for performing some special testing functions.

The utility program under development may be classified in terms of their degree of completion as: One, programs for which either code has been already written, or flow charts at the level of detail of code have been prepared; and two, those for which only general flow charts have been prepared, the charts being no more detailed than necessary to define the programs and demonstrate their feasibility.

The first category includes: 1. Subroutines for decimal to binary, and binary to decimal conversion, which are consistent with Maniac III arithmetic. For example, a decimal floating point number will be converted to a floating point binary number, in general non-normalized, having the following property: The number of leading zeros of the binary representation will be appropriate to the number of significant digits of the decimal representation. 2. A symbolic assembly program which will operate in one pass, using only high-speed memory. It has the property that the assembled program will exist in high-speed memory, ready to run, at the termination of assembly. Three-letter mnemonics are used for the operation codes. Acceptable address forms include decimal, hexadecimal, symbols of up to five characters, and program-point symbols. Arithmetic within address fields is restricted to addition of a signed decimal integer to the stated address form.

The second category includes: 1. A symbolic assembly program which will operate in several passes with the aid of magnetic tape storage. It will have several advantages over the one-pass assembler, the most notable being that all of high-speed memory will be available to the programmer. 2. A subroutine compiler. This program will do all of the bookkeeping necessary for the automatic use of relocatable library subroutines, including nesting of them to any depth. Thus, the programmer will be able to specify a closed subroutine by name at the appropriate point in the body of his symbolic code, and the compiler will determine where the subroutine is to be loaded, will load any needed sub-subroutines, plant all needed links, and ensure that no library routine is loaded more than once.

## 180 COMPUTER AND 180 DATA COLLECTOR - CONTROL DATA CORP. - MINNEAPOLIS. MINNESOTA

160 Computer. The 160 is a highly flexible, multi-purpose, stored program, small electronic digital computer the size of an ordinary office desk. It employs high speed (2-1/2 megacycle clock frequency) transistor amplifier circuits, diode logic, and a magnetic core matrix memory. It is intended for use in the fields of engineering calculations, statistical and business data processing, data conversion, data acquisition and logging, industrial control, and communications systems.

The main features are: parallel, binary mode of operation, one's complement arithmetic; 12-bit word length; 4,096 words of individually addressable magnetic core storage, with 6.4 microsecond storage cycle time, 2.2 microsecond read access time, and 12.8 microsecond add time including access time; single address logic, one instruction per word; direct, indirect, relative, and no addressing modes; 12-bit instruction word, 6-bit function code and 6-bit execution address.

Versatility is achived by 62 instructions and a complete programming package containing 22-, 33-, 44-bi. fixed point as Rhmetle. floating point, complex floating point, decimal, floating decimal, and an algebraic compiler. The average execution time is 15 microseconds per instruction. Execution times for typical subroutines are as follows: 22-bit addition in 185 microseconds; multiplication with 22-bit product in 1.0 milliseconds; division (22-bit x 22-bit) in 1.8 milliseconds; sines of X (using Taylor series expansion) through X quadruple precision (44 bits), average computation, one value, in 190 milliseconds; sorts 10,000 eightycharacter records, using four Ampex FR-300 tape units each operating at 30 kilocycles per second character rate, in 18 minutes. Equipments provided with the basic computer for input and output are a Ferranti punched paper tape reader (350 characters per second, up to 7 bits per character) and a Teletype high-speed paper tape punch (60 characters per second, up to 7 bits per character). Magnetic tape units employing Ampex model FR-400 or FR-300 tape handlers may be added as optional equipment. Tapes produced by these units are interchangeable with tapes from the CDC 1607 magnetic tape subsystem used with the 1604 computer, as well as tapes prepared by IBM 727 magnetic tape units. Information is written on and read from tape in 6-bit characters with appropriate parity checking procedures as part of the control associated with the individual tape unit. Tape running speed is 15,000 characters per second using the FR-400 transport.

A card read/punch unit may be connected by means of a card control unit containing the necessary assembly/disassembly, buffer, translation, and control circuitry. Data are read/punched a row at a time and transmitted to or from the 160 in 12-bit words. An Analex 56-160 line printer (1000 lines per minute, 120 character line) is available also as optional equipment.

Other optional input-output equipment can be connected to the computer by suitable buffer units. For example, the computer may be connected to a Teletype line for on-line operation by means of a buffer which provides for assembling and level-changing.

The 160 computer is constructed in a standard-size office desk which houses the computer circuitry, the F-rranti reader, and Teletype punch, and provides an operating console and visual display. Operating requirements are 500 watts of 110-volt, 60-cycle power, and a normal room-temperature environment.

One of the powerful applications of the computer is in CDC's "Satellite Computer System," a combination of their large-scale 1604 and the 160. One or more 160's are used in small, independently operated data processing centers which have <u>direct access</u> to the 1604. Thus used, the satellite 160's utilize the large capacity and high speeds of the 1604. In this system a <u>direct transfer feature</u> has been provided between the 1604 and the 160 without hooking up "black boxes." At any time, the 160 can interrupt the 1604 and transmit data to the large computer at the rate of 160,000 characters per second; data can be transmitted from the 1604 to the 160 at the same rate. Also by means of internal programming, data can be transferred from the 1604 to a magnetic tape unit which is directly available to the 160 (or vice vers 1). The 160 can accept this data from the <u>same</u> tape reel on the <u>same</u> tape drive used to transmit data to and from the 1604—thus eliminating the necessity of changing tape reels between computers.

180 Data Collector. The 180 Data Collector is a self-contained, portable device (about the size of a typewriter) designed to collect and record information in computer-intelligible form for later computer use. The equipment either eliminates entirely or substantially reduces the clerical labor now required to collect and record such data as payroll, work-in-process inventory, costs and scheduling, and time-clock records.

The unit automatically assembles into a punched paper tape <u>variable data</u> (such as job lot number, shrinkage, at amount produced), which is fed into the unit by 10 manually operated multi-position rotary switches on the front of the operating panel; <u>identification data</u> (such as employee number, machine number, and material identification), which is read selectively from pre-punched IBM cards by a card sensing unit that will accept up to 320 columns of information; <u>fixed data</u> (such as department number, plant location, and data collector station number), which is fed into the unit by 6 behind-panel multi-position rotary

switches available only to supervisory or maintenance personnel; and <u>time</u> from an internal clock. The internal clock provides and records time to the nearest 0.01 of an hour; a visual decimal unit displays this on the front panel.

The operator or clerk records the desired selectable data either at the beginning or end of each operation. Sequence control is automatic. A distributor scans the variable inputs, the input cards, the fixed data inputs and the clock, and translates from card code to output record code. The distributor also controls the output punch.

Error safeguards include a push-button which "voids" the preceding transaction, interlocks which assure proper sequence and a locked "on-off" switch which prevents accidental or illegal introduction of data. Also, a locked cover-plate guards the clock and the interior of the collector.

An automatic clock-in mode is provided to permit employees to use the collector as a time clock at the beginning and end of a shift. The internal clock automatically shifts from the <u>transaction mode</u> to the <u>clock-in mode</u> and vice versa.

The data output unit punches 16 characters per second on 8-level paper tape. Units of 5-, 6-, or 7-level are available optionally. The punched paper tapes collected from a number of 180's located throughout a facility may be processed by any standard, central computer to generate a variety of management reports.

Since each unit contains its own output paper tape recorder, the portability of the device is preserved as there is no need for expensive cabling for a communication system. Further, the fact that each unit contains its own output recorder materially speeds up the data recording operation by the elimination of recording bottlenecks.

Each unit is a modular self-contained unit that can be wall-mounted or placed on a table or desk. The unit is 16"h. x 17"w. x 13"d. and weighs 60 lbs. Single phase, 115 volts, 60-cycle power is required. A prototype installation has been in operation for severa! months and production units will be ready in the summer of 1960.

#### MANIAC II - LOS ALAMOS SCIENTIFIC LABORATORY - LOS ALAMOS, NEW MEXICO

A magnetic core memory with a capacity of 4096 49-bit words was added to the Maniac II computer at the Los Alamos Scientific Laboaatory in November 1959. It supplements the original electrostatic memory which employs a bank of 98 barrier grid tubes, and brings the total random access storage in the machine to 16,384 words.

Design of the memory was adapted from the coincident-current memory built by the Lincoln Laboratory for the Massachusetts Institute of Technology for its TX-2 computer. The Los Alamos version uses 80-mil cores and vacuum tube drivers. Controls, sense amplifiers, registers, and address decoders are transistorized. A total of 1149 transistors and 320 tubes is employed.

Cycle time in six microseconds and the interval between setting the memory address register and strobing the sense amplifier is 1.5 microseconds. Maniac II is an asynchronous single-sequence computer with internal speeds such that the core memory is usually able to complete its cycle before the next access is required. Addition of the new memory has increased program speeds by about 25 percent.

#### COMPUTER PROJECT - THE RICE INSTITUTE - HOUSTON, TEXAS

The Rice Institute Computer Project was organized at the Rice Institute in Houston, Texas in 1957, its prime objective being the design and construction of a high speed digital computer. Since the completed computer is to be used as a university research tool, the project was not placed within any one department, but organized as a separate group. This group is directed by a committee drawn from the various interested departments, and is directly responsible to the President of the Institute.

The computer project is being financed by the Atomic Energy Commission and the Shell Development Company. The engineering design is due almost entirely to original work done by members of the project staff. Tube, diode, and transistor circuits are each employed according to their suitability for the particular function. A 8192 word barrier-grid tube memory bank is now in operation, and it will be expanded to 32,000 words after the machine is in use. The word length is 56 bits, including 2 tag bits; a 48 bit mantissa and 6 bit exponent is used for number representation, and one instruction per word for orders. The floating point operations are performed in base 256 with a number range of  $10^{-75}$  to  $10^{+75}$  and an accuracy of 12 decimal digits. Floating point multiplication and division will take less than 100 microseconds. Input will be by punched tape at 40 words per second, and output on a fast line printer at ten 108 character lines per second. Magnetic tape units are buffered and will transfer information to or from the main memory at over 4,000 words per second.

The programming staff has assisted in the formulation of the order structure, and has completed a basic assembly routine, an algebraic assembly scheme, and a number of specialized subroutines. The order structure is a pseudo-three address system and is organized to facilitate use of the 6 B-Boxes and 4 Fast Storage Registers. Extensive trapping facilities are available for use in tracing routines, overflow detection, interpretation of orders, data, etc.

The computer has been under construction since September 1957, and is expected to be placed in routine operation within the next year.

## TRANSACTER SYSTEM - STROMBERG DIV., GENERAL TIME CORPORATION - THOMASTON, CONNECTICUT

The Stromberg TRANSACTER (TRANSACTion TransmittER) (See DCN, June 1960 is a new automatic all-purpose data-gathering device which serves as an information link between multiple, widely scattered transaction points and a central data- processing office, without the need of intervening paper work and clerical operations by humans. The transmitting speed is 60 characters per second.

The system consists of two parts: 1. Multiple, remotely operated TRANSACTERS (Transaction Transmission Stations), which will transmit up to 147 columns of transaction data by card input, identification data by card input, variable data by dial input, transaction codes by dial input, location identification by plugboard input, and programming instructions by plugboard input. 2. The central Compiler (Receiver-Recording Station). Depending on the volume, a suitable number of TRANSACTERS (up to a maximum of 50) may be connected to one Compiler. The Compiler will record all data transmitted by TRANSACTERS, record the exact time, date, and shift of the transaction, record end of message and program instructions for subsequent processing equipment, operate as a code converting unit, and select and switch TRANSACTERS to the output punching equipment.

Output is standard punched tape, suitable for immediate use in communications systems, automatic typewriters, punched tape-to-punched eard converters, or for direct input into electronic data-processing equipment.

Input media for the system are pre-punched cards or tags. In the preparation of the original hard copy, these cards can be produced automatically as a by-product of the typing operation, on standard data-processing equipment. They may also be drawn from master file or decks of repetitive information. These cards can be of 15,22, 29, 44, 58, and 80-column widths; made of punched card stock, tag or bristol paper, or plastic material, in thicknesses from .0067 to .030 inches.

From 10 to 50 TRANSACTERS can normally be connected to one Compiler, depending on the traffic, although this quantity is theoretically from one to over 50. The average number of TRANSACTERS connected to one Compiler will vary between 10 and 20. When one TRANSACTER has been set with the cards in position and the Compiler is busy, queueing is established by a stepping switch so that each input station is picked up automatically in turn.

The power requirements are 115 volts, 60 cycles The Compiler uses 1000 watts, and the TRANSACTER 500 watts.

#### UDOFTT - U. S. NAVAL TRAINING DEVICE CENTER - PORT WASHINGTON, N. Y.

The Universal Digital Operational Flight Trainer Tool system, UDOFTT (see DCN, January 1958) is undergoing final acceptance tests for the Navy and Air Force by a team from the Naval Training Device Center and Wright Air Development Center at Sylvania Electronic Systems, Waltham, Mass. After acceptance, the system will be shipped to Garden City, N.Y., where it will be used as a research tool in the field of flight simulation and training for both services (the Air Force and the Navy).

Discrete and shaft encoder inputs from a Navy F9F and an Air Force F100A simulated cockpit and instructor station, and outputs to the instruments in these cockpits and instructor stations are the primary communications with the computer during real time simulated flight. A stored program for each type of aircraft simulation, read in by conventional card reader, solves the aerodynamic, engine and aircraft system equations at a 20 cycles per second iteration rate to provide realistic instrument and control indications in the simulated aircraft cockpits.

#### COMPUTING CENTERS

#### ANALYSIS AND COMPUTATION DIVISION - AIR FORCE MISSILE DEVELOPMENT CENTER - HOLLOMAN AIR FORCE BASE, NEW MEXICO

The computing facility at AFMDC, consisting of two 1103-A's, the Data Assimilator (see DCN, July 1959), PACE analog computers, high speed analog-to-digital and digital-to-analog converters, and telemetry station, is in the process of being integrated into a comprehensive system capable of simultaneously handling analog and digital data in "real time."

At present, the system is used to speed up the digital data analysis of missions performed on this base. The information of two RF carriers of an FM/FM telemetry system (24 channels) is fed through the ground station, then digitized at a desirable sampling rate and picked up by one computer through Loading Platform One.

A practical demonstration of the feasibility of the "real time" concept is being prepared in cooperation with the Flight Simulation Laboratory, White Sands Missile Range. The purpose of the test is to evaluate the aerodynamic lift coefficient during an actual missile flight. The necessary data links are established and the direct processing of digitized radar information (FPS-16) is in the checkout phase. At present, the missile is simulated on the analog computer and the signals derived from this simulation are used to debug all the necessary data handling and digital computer evaluation processes.

## AEC COMPUTING AND APPLIED MATHEMATICS CENTER - NEW YORK UNIVERSITY - NEW YORK, NEW YORK

UNIVAC I. The Univac I computer has been turned off. The machine has been offered to all schools in this country, and several universities have indicated an interest in acquiring the computer.

IBM 704. Several unsponsored computing problems were approved for our IBM 704 in 1959. We are still able to consider requests for unsponsored computing which originates at non-profit institutions and which are in the mathematical and physical sciences.

## I'ACIFIC MISSILE RANGE - U. S. NAVAL MISSILE CENTER - POINT MUGU. CALIFORNIA

The Pacific Missile Range accepted its second Type 709 Computer on January 8, 1960 (see DCN, July 1959). Both computers are operated by Land-Air, Inc. under a contract administered by the Test Data Division. The new computer is installed at Point Mugu where it picked up the workload from its predecessor, an extended Type 650 phased out in March. The selection of components includes a 32,000 word core and 16 tape drives. Input-output is tape with off-line gear for card to tape, tape to card, and tape to high-speed printer.

The framework within which the new machine will be operated for data reduction is the specially designed Computer Utilization System (CUS). This system uses as much memory as possible and minimizes tape usage. The programmer using this system need not concern himself with either writing tape or with allocation of memory; this is done automatically for him. The programmer states what is to be done to the data, but not how.

Studies are not finished, but it appears that a data reduction process required from 1.05 to 1.10 times as long to be executed in CUS as a program written by an experienced programmer. The time to program, code and check-out a production run, however, will be about one-fifth as long. This parallels the performance of the Modular Operating Procedure (MOP) which was developed and used on the Type 650 by the same computing organization. CUS is scheduled for completion this spring.

Current data input to the computing center consists of cards generated by the Telereadex, Boscar, Richardson film readers, Oscarettes, and Mann Comparators. Unique input equipment which will bring this machine into real-time operations is nearing completion. High on the priority list is automatic aircraft vectoring which becomes possible with the PMR's new Data Multiplexing System (DMS). This system becomes the largest over-water microwave link yet attempted.

The 709 at Point Arguello is an 8,000 word core machine which was placed in service in August 1959. Its original assignment was the prediction of missile impact as a range safety service working from its choice of two AN/FPS-16 radar outputs. The output from the computer appears in a format for driving the plotting boards. This includes X-Y plots showing the predicted impact points on carefully drawn mylar charts. Shown also on these charts are slope fields for use in recognizing and judging potentially dangerous missiles in flight. Computations are adjusted for the effect of oblateness of the spheroid and also aerodynamic drag.

This machine is also to be programmed for COTAR input to yield information similar to that resulting from the AN/FPS-16 input. This new service will be provided by the computer simultaneously with and in addition to the present service. Other programming at this installation includes position versus time, statistical processes, and post-operational data reduction.

# COMPUTATION CENTER - U. S. NAVAL WEAPONS LABORATORY - DAHLGREN, VIRGINIA

IBM 7090. A steady increase in computing workload has led to the decision to install an IBM 7090 system in summer 1960.

NORC. Operation of the NORC, having been for some time on a 24-hour, 7-day basis, will be continued on an intensive schedule.

ADDAS. The Automatic Digital Data Assembly System (ADDAS) is being designed by the Naval Weapons Laboratory as a data link between remote receiving stations and the computer at the Operations Center (NWL) of the U.S. Navy Space Surveillance System being developed by the Naval Research Laboratory under sponsorship of the Advanced Research Projects Agency. The analog-digital conversion parts of the ADDAS are being designed by NRL and the digital by NWL. The system currently being constructed is a prototype for only one remote station; however, the system is designed to operate with up to 15 remote stations. At each

remote station approximately 20 channels of information will be digitized with a precision of one part in sixty-four at a rate of 20 samples per second, and transmitted over a telephone line in binary form at a rate of 2,500 bits per second. To distinguish observations of interest from unwanted observations, each observation of interest will be identified by a special code pattern (called the "alert" code) generated automatically by the equipment in the remote station. Data from all 15 stations will be combined in a single message assembly unit. The cut-put of the system is a tape for the NORC computer. The message assembler selects and records on the computer tape all data from any station for which the "alert" is present and in addition the five samples which precede the "alert" condition. In each sample recorded on computer tape the message assembler converts the data from binary to binary-coded decimal, inserts the station identification number, the time of the observation in days, hours, minutes, and seconds to one hundredth of a second; and arranges the data in a proper format for a NORC tape.

#### COMPUTERS AND CENTERS, OVERSEAS

#### ER 56 - STANDARD ELEKTRIK LORENZ AG - STUTTGART, GERMANY

The ER 56 is a fully transistorized, decimal sequence-controlled electronic computer. The building-block principle gives the possibility of combining installations of variable size and type of input and storage devices according to the requirements of scientific or commercial applications. A traffic pilot enables simultaneous operation—e.g., input and output operations can be carried out concurrently with arithmetic operations.

Arithmetic Unit. The Arithmetic unit performs the four elementary operations at fixed point for numbers of 6 or 13 decimal digits and at floating point for numbers of 11 decimal digits mantissa length. The internal representation of information is carried out in the decimal number system where the word length is 7 decimal digits. For fixed point numbers there are either 13 decimal digits plus sign (double word — e.g., automatic extraction of pairs of registers) or 6 decimal digits plus sign (single word). For floating point numbers there are 11 decimal digits plus sign, exponents of 2 decimal digits plus sign in the range of  $\pm$  49. Instructions are 7 decimal digits divided into: 4 digits, address; 1 digit, index; and 2 digits, operation. Outside of the arithmetic unit the 2 out of 5 code is used in the machine. Within the arithmetic unit the 1 out of 10 code is applied. Thus the circuitry of the arithmetic unit becomes very clear and easy to check. A faulty combination is detected by an automatic code check at each transfer of information.

Addition is by adding-matrices, subtraction is addition of tens complements, multiplication is by multiplying-matrix (automatic passing over of zeroes), and division is by subtraction or addition of multiples of the divisor as 4-2-2-1. There are three modes of operation: "Normal" in which the products and quotients are rounded; "Long" in which the products are full length, and quotients have remainders; and "Floating point" in which the products are full length, and quotients have remainders.

#### Operating Times (Milliseconds)

|                     | Fixed Point,         | Floating Point        |                                         |

|---------------------|----------------------|-----------------------|-----------------------------------------|

|                     | 6 Decimals Plus Sign | 13 Decimals Plus Sign | 11 Decimals Plus<br>Sign, Exponent ± 49 |

| Writing, Storing    | 0.14                 | 0.22                  | 0.22                                    |

| Adding, Subtracting | 0.20                 | 0.30                  | 0.961.10                                |

| *Multiplying        | 0.320.67             | 0. 62 2. 30           | 0.822.26                                |

| Dividing            | 2.96                 | 9.75                  | 7.98                                    |

| Comparing           | 0.18                 | 0.34                  | 0.34                                    |

<sup>\*</sup>By passing over zeroes, multiplication time is cut according to the number of zeroes in the multiplier.

<u>Control Unit</u>. The control unit controls the interconnection of the individual operating units and the correct sequencing of instructions during a program. It also contains address modification facilities, thereby making it possible to modify addresses independently of the main arithmetic unit. There are 9 index registers, one of which serves as control counter, and one as return address register. Address-modification is by adding-matrices.

<u>Instructions</u>. The instructions are of the one-address type. The order code comprises about 140 instructions. This large number enables the programmer to write short and clear programs.

Ferrite Core Working Store. The Ferrite Core Working Store consists of several independent storage sections. They may also be used as buffer stores for the input and output equipment, as well as for block transfers to and from the backing stores. There are storage sections for 200 or 1000 words of any combination up to a maximum of 10,000 words. The access time is less than 10 microseconds. Since this is less than one pulse duration time it is considered negligible.

Traffic Pilot. The Traffic Pilot, especially developed for the ER 56, can connect each of the ferrite core storage sections to each of the operating units. Several such connections may exist simultaneously between different storage sections and operating units. Block transfers to and from backing stores, input-output operations as well as the actual computation can be carried out at the same time. This cuts down total computer time.

Power Supply. 220/380 V. three phase a-c with neutral and earth, 47-55 cps. Other values are available upon request. The average power consumption is 4 kilowatts.

Backing Stores. 1. Magnetic drum with a capacity of 12,000 words — half-capacity can be supplied. Average access time is 10 milliseconds. The magnetic inscription is 0.23 mm bit spacing and 1.19 mm track spacing. 2. Magnetic tape with a capacity (per 1000 m tape) of 2 million words. The tape width is 25 mm and the speed is 9000 words per second.

Input Devices. 400 cards per minute by photoelectric punched-card reader, 200 or 400 characters per second by photoelectric punched-tape reader, and up to 63,000 characters per second by magnetic tape.

Output Devices. 50 characters per second by tape perforator, 7 characters per second by teleprinter, 100 cards per minute by card punch, 100 characters per second by mosaic printer, 600 to 2,850 characters per second by high speed line printer, and up to 63,000 characters per second by magnetic tape.

Physical Characteristics. The cabinets are 4'10" l. x 1'5" w. x 7'4"h., and weigh 1000 lbs. The main power pack is 4'3" l. x 1'9" w. x 4'4" h., and weighs 1000 lbs. The control desk is 6'l. x 3" w. x 2'6" h., and weighs 450 lbs. The operator's console is 3'9" l. x 1'w. x 10" h. The desk for input and output equipment is 4'2" l. x 2' w. x 2'3" h.

#### **MISCELLANEOUS**

#### CONTRIBUTIONS FOR DIGITAL COMPUTER NEWSLETTER

The Office of Naval Research welcomes contributions to the NEWSLETTER. Your contributions will assist in improving the contents of this newsletter, and in making it an even better medium of exchange of information, between government laboratories, academic institutions, and industry. It is hoped that the readers will participate to an even greater extent than in the past in transmitting technical material and suggestions to this Office for future issues. Because of limited time and personnel, it is often impossible for the editor to acknowledge individually all material which has been sent to this Office for publication.

The NEWSLETTER is published four times a year on the first of January, April, July, and October, and material should be in the hands of the editor at least one month before the publication date in order to be included in that issue.

The NEWSLETTER is circulated to all interested military and government agencies, and the contractors of the Federal Government. In addition, it is being reprinted in the Communications of the Association for Computing Machinery.

Communications should be addressed to:

GCRDON D. GOLDSTEIN, Editor Digital Computer Newsletter Information Systems Branch Office of Naval Research Washington 25, D. C. Gevernment regulations require the maintenance of up-to-date distribution lists for all periodicals. The form below is for your convenience to indicate necessary changes or corrections. Do not return this sheet if your present listing is correct. Please send to Code 437, Office of Naval Research, Washington 25, D. C.

| TO: DIGITAL COMPUTER NEWSLETTER, Code 437, Office of Naval Research, Washington 25, D. C.                                   |                     |  |  |  |  |

|-----------------------------------------------------------------------------------------------------------------------------|---------------------|--|--|--|--|

| REVISE AS INDICATED BELOW                                                                                                   |                     |  |  |  |  |

| DELETE FROM DISTRIBUTION LIST                                                                                               |                     |  |  |  |  |

| (Please print or type)                                                                                                      |                     |  |  |  |  |

| From: PRESENT ADDRESS (A complete copy of the present name and address, as it appears on the envelope, MUST be listed here) | TO: CORRECT ADDRESS |  |  |  |  |

| SI GNATURE                                                                                                                  | DATE                |  |  |  |  |