⟨⟨,

# DIGITAL COMPUTER

#### MATHEMATICAL SCIENCES DIVISION OFFICE OF NAVAL RESEARCH

Vol. 14, No. 3

Gordon D. Goldstein, Editor

July 1962

16

25

CONTENTS

- EDITORIAL NOTICES

1. Editorial Policy

2. Policy for Contributions

3. Circulation Policy

# COMPUTERS AND DATA PROCESSORS, NORTH AMERICA 1. Advanced Scientific Instruments, Inc., ADVANCE II, ASI-420 and ASI-210, Minneapolis 22, Minnesota 2. Bendix Computer Division, Multiple-Processor G-21, Los Angeles, California 3. Control Data Corporation, Control Data 3600, Minneapolis 20, Minnesota 4. Control Data Corporation, Control Data 6600, Minneapolis 20, Minnesota 5. Electronic Associates, Inc. HYDAC SERIES 2000-Hybrid Digital/Analog Computer, Long Busand, Naw Lorses. Lectronic Associates, Inc. ATDAC SERIES 2000-Hybria Digital Analog Compute: Long Branch, New Jersey International Business Machines Corporation, IBM 7094, White Plains, New York Scientific Data Systems, 900 Series Computers, Santa Monica, California U.S. Army Ballistic Research Laboratories, Computing Laboratory, BRLESC, Aberdeen Proving Ground, Maryland

COMPUTING CENTERS

National Bureau of Standards, Recording Physiological Measurements for Data

Processing, Washington 25, D. C.

Ordnance Tank Automotive Command, New Computing Systems, Detroit 9, Michigan

Naval Ordnance Laboratory, Mathematics Department, White Oak, Silver Spring, Maryland

4. U.S. Naval Underwater Ordnance Station, Analysis Branch, Newport, Rhode Island

5. U.S. Naval Weapons Laboratory, Computation Center, Dahlgren, Virginia

6. U.S. Navy David Taylor Model Basin, Flame Program, Washington 25, D. C.

7. U.S. Navy David Taylor Model Basin, Performance Data for LARC System, Washington 25, D. C.

COMPUTERS AND CENTERS, OVERSEAS

1. Institut Für Angewandte Mathematik, Johannes Gutenberg-Universität, Siemens 2002, Mains, Germany

Leo Computers, Ltd., LEO III Time-Sharing, London, England

Leo Computers, Ltd., LEO III/F, London, England

Leo Computers, Ltd., LEO Document Reader, London, England

National Physical Laboratory, Autonomics Division, An Artificial Language for

Information Retrieval, Teddington, Middlesex, England 39

MISCELLANEOUS

1. Cornell Aeronautical Laboratory, Inc., Multi-Font Character Recognition, Buffalo, New York

2. A.B. Dick Company, High-Speed Videograph Printer-Plotter, Chicago 48, Illinois

3. Honeywell EDP Division, Auto-Corrective Optical Scanner, Wellesley Hills, 81, Massachusetts

Memistor Corporation, Auto-corrective Optical Scanner, well-sley Hill

Massachusetts

Memistor Corporation, The M-2CR Memistor, Mountain View, California

The National Cash Register Co., Photochromic Dynamic Display,

Hawthorne, California

46 Penn Sate and IBM, Home-Study Course in Computer Programming,

University Park, Pennsylvania

Symposium on Optical Character Recognition, 15-17 January 1962, Washington, D. C.

University of Illinois, PLATO II, Urbana, Illinois

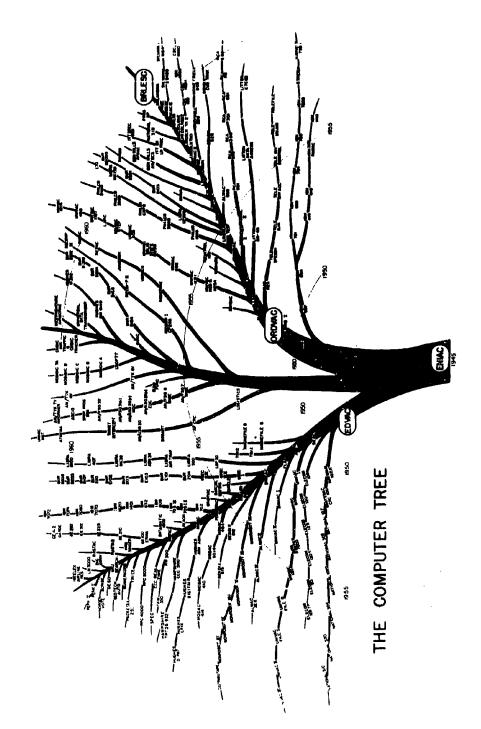

U.S. Army Ballistic Research Laboratories, Computing Laboratory, The Computer

Trac. Aberdsen Proving Grand Maryland

Tree, Aberdeen Proving Ground, Maryland

Approved by The Under Secretary of the Navy 25 September 1961

NAVEXOS P-645

Reproduced by the CLEARINGHOUSE for Faderal Scientific & Technical Information Springfield Va. 22151

The discursion has been approved for public referee and sale; its distribution is unlimited

## **EDITORIAL NOTICES**

#### **EDITORIAL POLICY**

The Digital Computer Newsletter, although a Department of the Navy publication, is not restricted to the publication of Navy-originated material. The Office of Naval Research welcomes contributions to the Newsletter from any source. The Newsletter is subjected to certain limitations in size which prevent publishing all the material received. However, items which are not printed are kept on file and are made available to interested personnel within the Government.

DCN is published quarterly (January, April, July, and October). Material for specific issues must be received by the editor at least one month in advance.

It is to be noted that the publication of information pertaining to commercial products does not, in any way, imply Navy approval of those products, nor does it mean that Navy vouches for the accuracy of the statements made by the various contributors. The information contained herein is to be considered only as being representative of the state-of-the-art and not as the sole product or technique available.

#### POLICY FOR CONTRIBUTIONS

The Office of Naval Research welcomes contributions to the Newsletter from any source. Your contributions will provide assistance in improving the contents of the publication, thereby making it an even better medium for the exchange of information between government laboratories, academic institutions, and industry. It is hoped that the readers will participate to an even greater extent than in the past in transmitting technical material and

suggestions to the editor for future issues. Material for specific issues must be received by the editor at least one month in advance. It is often impossible for the editor, because of limited time and personnel, to acknowledge individually all material received.

#### CIRCULATION POLICY

The Newsletter is distributed, without charge, to interested military and government agencies, to contractors for the Federal Government, and to contributors of material for publication.

For many years, in addition to the ONR initial distribution, the Newsletter was reprinted by the Association for Computing Machinery as a supplement to their Journal and, more recently, as a supplement to their Commun' ations. The Association decided that their Communications could better serve its members by concentrating on ACM editorial material. Accordingly, effective with the combined January-April 1961 issue, the Newsletter became available only by direct distribution from the Office of Naval Research.

Requests to receive the Newsletter regularly should be submitted to the editor. Contractors of the Federal Government should reference applicable contracts in their requests.

All communications pertaining to the Newsletter should be addressed to:

> GORDON D. GOLDSTEIN, Editor Digital Computer Newsletter Informations Systems Branch Office of Naval Research Washington 25, D. C.

### COMPUTERS AND DATA PROCESSORS, NORTH AMERICA

ADVANCE II, ASI-420 AND ASI-210— ADVANCED SCIENTIFIC INSTRUMENTS, INC., MINNEAPOLIS 22, MINNESOTA

Advanced Scientific Instruments, Inc., has designed three computers which cover the field

in computing and data processing capability. They are, in order of decreasing size, the ADVANCE II, the ASI-420, and the ASI-210

All three machines are high speed, parallel, internally programmed, solid-state

computers with random access core memories having a iotal cycle time of 2 microseconds, including addressing of the next word. All of the computers have extensive input-output buffering facilities which make them adaptable to real-time applications, and which permit the integration of large quantities of peripheral equipment.

To date ASI has delivered one 210 to Goddard Space Flight Center, one 210W (a modified 210) to Argonne National Laboratory, and has announced the sale of another to Chance Vought Corporation.

The 210 system sold to Chance Vought carries a price tag of \$113,000. The medium scale ASI-420 sells for \$324,000, and the larger scale ADVANCE II for \$860,000.

#### Programming

The instructions used in all ASI computers are divided into two classes, termed class A and class B. Class A instructions are used universally in all three machines, and programs prepared with class A instructions can be executed on any ASI machine. Class B instructions are used only with the larger ASI-420 and ADVANCE II computers; programs prepared with the class B instructions can be executed without modification only on the larger machines.

#### Input-Output

The input-output system of the ADVANCE II computer consists of several input-output assembly registers and an independent control system. Information can be exchanged between the computer and external devices completely independently of arithmetic operations, and the input-output system can provide off-line communications between items of peripheral equipment. The total information transfer rate of the ADVANCE II input-output system is 250,000 words per second. Additionally, the ADVANCE II has a direct, high speed input-output channel capable of 500,000 42-bit word transfers per second.

The ASI-420 and ASI-210 computers also use input-output assembly registers for external communication, but these are controlled by the central control system. The transfer of a block of information is initiated with a single instruction. Thereafter, each assembly register is serviced by the memory during specific times set aside for this purpose in all instructions, and the program is not further affected by the transfer. In other words, the memory is

time shared by the arithmetic and input-output sections of the computer.

Either fixed or variable block transfers are made possible by two memory address registers associated with each assembly register. One of these registers contains the address of the first word of the block, and the other contains the address of the last word of the block. With the transfer of each word, the first register is incremented. When the contents of the registers are identical, the block has been transferred and input-output operation ceases. The size block can be varied simply by the addresses entered originally into the address registers.

#### Advance II

The ADVANCE II computer is a 42-bit machine with a memory expandable to 32,768 words. The computer has an optional maximum of eight buffered input-output channels with a combined transfer rate of 250,000 words per second. Arithmetic speeds of the computer

| Operation | Speed (µsec) |

|-----------|--------------|

| add       | 6            |

| multiply  | 33           |

| divide    | 33           |

The speed of the machine is enhanced by an instruction look-ahead feature in which the next instruction of a program is extracted from the memory, and indexing of the operand is performed while the current instruction is being executed. This operation is performed simultaneously with arithmetic operations because the memory address register is not used in arithmetic functions, and the indexing addition is performed in an independent 15-bit adder. When the current instruction is completed, the next instruction is immediately ready.

An 84-bit, 512-word magnetic core memory stores micro-program commands from which the instructions of the computer are constructed. The operation code of an instruction is translated to the address of the first command in the micro-program memory. Thereafter, the memory is stepped through successive memory locations, and the resultant commands complete the instruction. Any command or sequence of commands can be repeated under control of a repeat counter.

The micro-program memory can be filled or replaced from either the main memory or the paper tape reader of the computer. Instruction substitutions can be made easily, and unique instructions for specific applications can be formulated from the available micro-commands. This feature provides the ADVANCE II with exceptional flexibility.

One of the most powerful features of the ADVANCE II is its ability to communicate with other ASI computers in multi-computer complexes. Such communication can be effected both through the real-time, high-speed, input-output channels and through the buffered channels. Each computer regards the other merely as external devices, and through the facilities of the trapped interrupt, can be alternately isolated from the other computers or enabled to participate, all under program control. In this way, "executive privilege" for one computer is not necessary, and independent computer programs can be "merged" effectively. Intercomputer communication is made possible simply by wiring, and no auxiliary electronics is required.

#### AST-420

The ASI-420 is a 42-bit machine with a memory expandable to 16,384 words. The computer has an optional maximum of six input-output buffer channels with a combined transfer rate of 125,000 words per second. Arithmetic speeds of the machine are:

| Operation | Speed (µsec) |

|-----------|--------------|

| add       | 10           |

| multiply  | 64           |

| divide    | 98           |

The speed of the ASI-420 is less than that of the ADVANCE II because of the time allowed in each instruction to service the input-output buffer registers. This time is allowed whether or not input-output data is transferred, and remains the same regardless of the number of channels used. Therefore, the transfer rate of 125,000 words per second is constant for machines with any number of buffer channels.

#### AST-210

The ASI-210 is a general purpose, high speed, solid-state digital computer of small size. It is well suited to applications in scientific and engineering computations, data reduction, and real-time process control. The ASI-210 has the following outstanding features:

- Stored program, parallel operation, solid-state circuits, 21-bit word length, and magnetic core memory expandable to 8192 words.

- 2. Buffered input-output channels with total transfer rate of 62,500 21-bit words per second. Number of buffered channels is one, with one additional channel optional. Buffers can be used in an effective manner off-line for conversion operations.

- 3. Multiple indexing using index words stored in the computer memory.

- Indirect addressing. Successive indirect addressing is possible with indexing at each step.

- 5. Trapped interrupt. Logic circuits, which sense interrupt events, can be armed or disarmed under program control to jump the program into corresponding sub-routines upon occurrence of the event. The trapped interrupt feature saves a great deal of time and memory in programs because the interrupt conditions do not have to be tested repeatedly. It is also useful in cases where two or more computers are used together in the same system, or where a computer converses with several items of peripheral equipment.

- 6. One-megacycle phase rate operation. Add time 10 microseconds; multiply time 54 microseconds, including indexing and memory access time.

- 7. Six sense switches. Program branching may be controlled by sense switches on the operators console.

- 8. No air conditioning is required. High reliability operation in extreme temperature and humidity conditions. Equipment is designed to operate in ambient 32° to 125°F at 95 percent relative humidity.

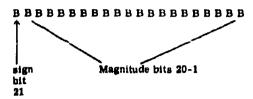

#### **Number Format**

B represents 1 binary digit.

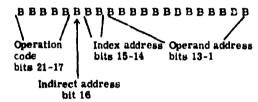

#### INSTRUCTION FORMAT

Instruction Word

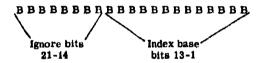

#### **Index Word**

B represents 1 binary digit.

#### Instruction List

#### Notation

- Register A is the accumulator

- E Register E is a second major arithmetic register

- () Contents of, for example, (A) signifies the contents of the A register

- + Add

- Subtract

- . Multiply

- . Divide

- "is placed in"

Absolute value, for example. (A) signifies the absolute value of the contents of the A register

Complement of, for example, (A) signifies the complement of the contents of the A register

- ⊕ Logical OR, for example, (Ē) ⊕ (m) signifies the logical OR of the complement of the contents of the E register and the operand

- Logical AND, for example, (E) @

(m) signifies the logical AND of the

contents of the E register and the

operand

- a Register A designator in the operand address

- e Register E designator in the operand address

- s Shift right designator

- c Shift circular designator

- g Gray to binary shift indicator

- k Shift count

- Ib Index base

- p Effective operand address

- m The memory location specified by p

- i Address of present instruction

- (m) Operand

Unless otherwise indicated, the operand address is subject to indexing and indirect address.

#### Arithmetic

The adder used in the ASI-210 is a closed loop binary adder using left end-around carry operation in the one's complement addition. The sign bit (21) is a zero (0) for positive numbers and a one (1) for negative numbers. This is useful in most operations using the entire register A. However, in certain instances such as indexing, only a small portion of the adder is used and provisions to prevent end-around carry are made. Operation is then carried out

4

in the two's complement addition which gives the correct answer without carry. A comparison of the two systems is shown:

| Decimal        | Binary | 1's Comp. | 2's Comp.      |  |

|----------------|--------|-----------|----------------|--|

| <b> </b> →3    | 011    | +3        | +3             |  |

| 2              | 010    | +2        | +2<br>+1<br>+0 |  |

| 1              | 001    | +1        |                |  |

| 0              | 000    | +0        |                |  |

| 7              | 111    | -0ª       | -1             |  |

| 6              | 110    | -1        | -2             |  |

| 5 101<br>4 100 |        | -2        | -3             |  |

|                |        | -3        | -4             |  |

a-0 is meaningless. All carries are forcibly entered in adder so that the number becomes 000 or +0.

#### ASI-210 Instruction Chart

| Octal Code | Instruction       | Including Index<br>& I/O Time<br>(µsec) | Not Including Index<br>& I/O Time<br>(µsec) |  |

|------------|-------------------|-----------------------------------------|---------------------------------------------|--|

| 00         | HALT              | 8                                       |                                             |  |

| 02         | JUMP              | l š                                     | 4                                           |  |

| 04         | RETURN            | 12                                      | 8                                           |  |

| 06         | END INTERRUPT     | 8                                       | 4                                           |  |

| 10         | ADD               | 10                                      | 6                                           |  |

| 12         | SUBTRACT          | 10                                      | 6                                           |  |

| 14         | LOAD A            | 10                                      | 6                                           |  |

| 16         | LOAD E            | 12                                      | 8                                           |  |

| 20         | ABSOLUTE VALUE    | 8                                       | 4                                           |  |

| 22         | NEGATE            | 8                                       | 4                                           |  |

| 24         | CLEAR             | 12                                      | 8                                           |  |

| 26         | STORE A           | 8                                       | 6                                           |  |

| 30         | MULTIPLY          | 54                                      | 50                                          |  |

| 32         | DIVIDE            | 56                                      | 52                                          |  |

| 34         | ROUND             | 14                                      | 10                                          |  |

| 36         | STORE A ADDRESS   | 10                                      | 6                                           |  |

| 40         | COMPARE < A       | 14                                      | 10                                          |  |

| 42         | COMPARE = A       | 14                                      | 10                                          |  |

| 44         | TEST A < 0        | 10                                      | 6                                           |  |

| 46         | STORE E           | 10                                      | l 6                                         |  |

| 50         | AUGMENT INDEX     | 12                                      | 12                                          |  |

| 52         | TEST INDEX        | 10                                      | 10                                          |  |

| 54         | STORE ADDRESS     | 12                                      | 12                                          |  |

| 56         | LOGICAL OR        | 12                                      | 10                                          |  |

| 60         | SHIFT             | 10+2K                                   | 6+2K                                        |  |

| 62         | NORMALIZE A       | 14+2K                                   | 10+2K                                       |  |

| 64         | NORMALIZE A, E    | 14+2K                                   | 10+2K                                       |  |

| 66         | LOGICAL AND       | 12                                      | 10                                          |  |

| 70         | TRAP              | 8                                       |                                             |  |

| 72         | SENSE SWITCH      | 10                                      | 6                                           |  |

| 74         | EXTERNAL DEVICE   | 16                                      | 12                                          |  |

| 76         | ASSEMBLY REGISTER | 20                                      | 16                                          |  |

**Explanation of Instructions**

$$\dot{U}$$

ADD  $(A) + (m) \longrightarrow A$

Add the operand to (A). The sum will appear in Register A. This instruction can result in an add overflow.

12 SUBTRACT (A) - (m)

$$\rightarrow$$

A

Subtract the operand from the contents of A. The difference will appear in Register A. This instruction can result in an add overflow.

$$MULTIPLY (A) \cdot (m) \longrightarrow AE$$

Multiply the contents of A by the operand. The most significant bits of the product will appear in Register A and the least significant bits in Register E.

32 DIVIDE (AE)

$$\div$$

(m)  $\longrightarrow$  E rem  $\longrightarrow$  A

Divide the contents of A and E by the operand. The quotient will appear in Register E and the remainder in Register A. A fault interrupt may occur if the contents of A is greater than or equal to the operand.

24 CLEAR

$$0 \rightarrow A$$

, or  $0 \rightarrow E$ , or  $0 \rightarrow AE$

Clear A if the a designator bit 12 of the operand address is a 1. Clear E if the e designator bit 11 of the operand address is a 1. Clear A and E if the a and e designator bits 12, 11 of the operand address are 1's.

22 NEGATE

$$(\overline{A}) \longrightarrow A$$

, or  $(\overline{E}) \longrightarrow E$ , or  $(\overline{AE}) \longrightarrow AE$

Complement the contents of Register A if the a designator bit 12 of the operand address is a 1. Complement the contents of Register E if the e designator bit 11 of the operand address is a 1. Complement the contents of Register A and E if the a and e designator bits 12, 11 of the operand address are 1's.

20 ABSOLUTE VALUE

$$|(A)| \longrightarrow A$$

, or  $|(E)| \longrightarrow E$ , or  $|(AE)| \longrightarrow AE$

Make the contents of A positive if the a designator bit 12 of the operand address is a 1. Make the contents of E positive if the e designator bit 11 of the operand address is a 1. Make the contents of A and E positive if the a and e designator bits 12, 11 of the operand address are 1's.

Add the most significant bit of Register E to the contents of A in the least significant bit. The result will appear in Register A. Register E will be unchanged.

36 STORE A ADDRESS

$$(A_{13-1}) \longrightarrow (m_{13-1})$$

Stores operand address portion of (A) in the operand address portion of the operand (m).

Transfer

Bring the operand to Register A.

Bring the operand to Register E.

26

STORE A  $(A) \longrightarrow m$

Store the contents of A in the memory location specified by the operand address.

46

STORE E (E)→m

Store the contents of E in the memory location specified by the operand address.

60

SHIFT

| Bit                            | 12 | 11       | 10 | 9  | 8   | 7-1          |

|--------------------------------|----|----------|----|----|-----|--------------|

| Designator                     | a  | e        | В  | _c | g   | <u>_ k</u>   |

| SHIFT (A) RIGHT                | x  | 1        | ×  |    |     | <sub>x</sub> |

| SHIFT (A) LEFT                 | x  |          | ^  |    |     | â            |

|                                | 1  |          | {  |    |     | â            |

| SHIFT (A) LEFT CIRCULAR        | ×  | !        |    | X  |     |              |

| SHIFT (E) RIGHT                | ļ  | X        | x  |    |     | x            |

| SHIFT (E) LEFT                 | 1  | X        |    | ĺ  | ì   | x            |

| SHIFT (E) LEFT CIRCULAR        |    | х        |    | x  |     | x            |

| SHIFT (AE) RIGHT               | x  | x        | ж  |    |     | x            |

| SHIFT (AE) LEFT                | x  | x        |    | ŀ  | ĺ   | x            |

| SHIFT (AE, LEFT CIRCULAR       | X  | x        | 1  | x  |     | x            |

| CONVERT (E) FROM GRAY CODE TO  |    | į        |    |    | x   | x            |

| BINARY LEAVING THE RESULT IN A | L  | <u> </u> | L  | L  | 14. |              |

See "INSTRUCTION LIST, Notation" for definition of designators a through k.

Right shifts are open-ended shifts. Left shift may be either open-ended or circular shifts. In open-ended shifts, the bits introduced into the register are identical to the sign bit 21 which remains unchanged. In circular shifts, the sign bit 21 is shifted along with the number. The number of shifts, specified by the shift count (k), cannot exceed 63 decimal  $(2^6-1)$ .

62 NORMALIZE A (A)

$$\cdot$$

2<sup>k</sup> until A20  $\neq$  A21, and,  $k + (m) \longrightarrow m$

Shift the contents of A left, leaving the sign bit 21 unchanged, until the sign bit 21 and the most significant bit 20 are different. With each shift, the sign bit will be entered in the least significant bit 1 of A and the most significant bit 20 of A will be lost. Add the number of shifts required to the operand address portion of the operand specified by the operand address.

64 NORMALIZE A AND F (AE)

$$\cdot$$

2<sup>k</sup> until A20  $\neq$  A21, and, k + (m)  $\longrightarrow$  m

Shift the contents of A and E left, leaving the sign bit 21 unchanged, until the sign bit 21 and the most significant bit 20 of A are different. With each shift, the sign bit 21 of E will be entered in the least significant bit 1 of E, and the most significant bit 20 of E will be entered into the least significant bit 1 of A. The most significant bit 20 of A will be lost. Add the number of shifts required to the operand address portion of the operand specified by the operand address.

66 LOGICAL AND

$$(E) \odot (m) \longrightarrow A$$

Form the logical "and" of the operand and the contents of E in Register A. An example of the bitfor-bit result is as follows:

> Contents of E 1100 Operand 1010 Logical and 1000

#### LOGICAL OR (E) $\oplus$ (m) $\longrightarrow$ A.

bit result is as follows:

56

50

Form the logical "or" of the operand and the contents of E in Register A. An example of the bit-for-

1100 Contents of E Operand Logical or

AUGMENT INDEX p + Ib -- Ib

Add the specified operand address to the index base, and replace the index base with the sum. This instruction can result in an index overflow. The addition will be in the two's complement system. This instruction permits decrementing as well as incrementing.

SKIP IF INDEX HIGH

The specified operand address of this instruction is the complement of the index limit address. This limit address is in one's complement if the limit is positive, and in two's complement if the limit is negative. When the index base (contents of the index register in two's complement format) exceeds the limit address, the next instruction in sequence will be skipped. . .otherwise the instructions will continue in sequence. The skip will occur when the addition of the 13-bit limit address with the 13-bit index base causes a carry into the 14th bit position.

#### Examples

If the index base exceeds four and it is desired to skip, the index limit address will be:

1 1 1 1 1 1 1 1 1 1 0 1 1 (Binary - one's complement)

Bit X 0 0 0 0 0 0 0 0 0 0 1 0 1 Index Base Index Limit X111111111111111 X1111111111011 X 1 1 1 1 1 1 1 1 1 1 1 1 1 1 100000000000000 Sum No skip occurs when Skip occurs when index base = 4 index base = 5

If the index base exceeds -4 and it is desired to skip, the index limit address will be:

0 0 0 0 0 0 0 0 0 0 0 1 1 (Binary - two's complement)

Bit X 1 1 1 1 1 1 1 1 1 1 1 0 1  $\begin{array}{c} \underline{Bit} \\ \overline{X} \ \ 1 \ \ 1 \ \ 1 \ \ 1 \ \ 1 \ \ 1 \ \ 1 \ \ 1 \ \ 1 \ \ 0 \ \ 0 \end{array}$ X0000000000011 Index Limit X000000000011 Sum X111111111111111 100000000000000 No skip occurs Skip occurs when when index base = -4 index base = -3

(in two's complement) (in two's complement) (i.e., if the limit desired is a negative number, the rule is the following:

|limit| -1 = index limit address)

# 04 RETURN 1 + 2 -- m 1 thru 13

Store the address of the instruction following the next sequential instruction in the operand address of the operand. By letting the operand be a jump instruction at the end of a sub-routine, the program can jump into the subroutine on the next instruction and return to its program sequence at the end of the sub-routine.

#### 02 JUMP

Take (m) as the next instruction.

#### 00 HALT

Halt, and take (m) as the next instruction when operation is resumed.

40 COMPARE

$$<$$

A (m)  $<$  (A), skip and take  $i+2$  (m)  $\geq$  (A), take  $i+1$

If the operand is less than the contents of A, skip the next instruction of the sequence.

42 COMPARE = A (m) = (A), skip and take

$$i + 2$$

(m)  $\neq$  (A), take  $i + 1$

If the operand equals the contents of A, skip the next instruction of the sequence.

#### 44 TEST A < 0

If (A) are less than 0, take next instruction from operand.

#### 54 STORE ADDRESS IN INDEX p→I<sub>h</sub>

Store the operand address in the base address portion of the memory location specified by the index address. The operand address will not be indexed.

#### 06 END INTERRRUPT

Take (m) as the next instruction, then discontinue the interrupt. This instruction must be used at the end of an interrupt routine.

#### 70 TRAP

If bit 12 of the operand address is a "1," the contents of the trap flip-flops will be stored in operand address portion of register A in the bit positions specified below. If bit 11 is a "1," the specified traps will be armed. If bit 10 is a "1," the specified traps will be disarmed. If bit 13 is a "1," the contents of the Add overflow and

Index everflow flip-flops may be stored in the bits of A corresponding to their trap designators. These two flip-flops will be reset by recognition of interrupt or by storage in A as described. Bit specification of the operand address of the Set Trap instruction:

- 13 Store flip-flop designator

- 12 Store trap designator

- 11 Arm trap designator

- 10 Disarm trap designator

- 1 External device interrupt trap

- 2 Busy interrupt trap

- 3 Operator interrupt trap

- 4 Fault interrupt trap

- 5 Add overflow interrupt trap

- 7 Index overflow interrupt trup

- 8 Operator control light 1

- 9 Operator control light 2

#### 74 EXTERNAL DEVICE

Interpret the operand as an external device control word (EDCW). A busy interrupt could result from this instruction. The external device control word is described in detail under external device instruction.

#### 72 SENSE SWITCH

If any of the sense switches 1-6 specified in the operand address bits 1-6 is set, skip the next instruction in the normal sequence. If the next instruction is a jump instruction, this is in effect a programmed jump that is conditional upon the sense switches. These switches may be changed at any time by the operator. If more than one sense switch is specified, the skip will occur if any of the specified switches is set.

#### 76 ASSEMBLY REGISTER

Interpret the operand as an assembly register control word (ARCW). A busy interrupt can result from this instruction. The assembly register control word is described in detail under assembly register instruction.

#### Trapped Interrupt

A number of events can cause the program of the computer to be interrupted. Some of these are:

Busy Operator

Add Overflow External device

Fault Index overflow

An interrupt trap associated with each event may be set under program control to either respond when the event occurs or to ignore it. The traps are controlled by the "trap" instruction. Bits 11 and 10 in the operand address designate whether the specified traps will be armed or disarmed, and bits 9 through 1 of the operand address specify which traps (or indicator flipflops) are to be armed (set) or disarmed (cleared). If bit 12 of the operand address is present the condition of each of the traps will be stored in the operand address portion of register A in the bit position that corresponds to the designating bit for that particular trap in the "trap" instruction. This will occur before any changes are made in these conditions as a result of bit 11 or 10 occurring in the same "trap" instruction. This is very useful in sub-routines that require the use of these traps, but that also must return these traps to their previous condition at the end of the sub-routine.

By specifying bit 13 in the trap instruction, the contents of the Add overflow and Index overflow flip-flops may be stored in the bits of A corresponding to their trap designators. These three flip-flops will be reset by recognition of interrupt or by storage in A as described,

If a particular trap is set to respond to the occurrence of an event, an interrupt is initiated when the event occurs (and the interrupt routine flip-flop is set). As a result of this interrupt, the current instruction will be completed and the address of the following instruction will be stored in the interrupt fixed address (00110). Then control is transferred to a unique fixed address (identified below) associated with the particular event or condition which caused the interrupt. The contents of the unique fixed address will usually be a jump instruction leading to a sub-routine. Thus, the programmer may have a different sub-routine for each event that may cause an interrupt. The sub-routines will be entered without the necessity of the programmer writing a decoding program to find which sub-routine to enter since the occurrence of a particular interrupt causes a jump to a particular sub-routine. At the end of each sub-routine is a jump to the interrupt fixed address (00110). In the interrupt fixed address is an "end interrupt" instruction which is identical to a jump instruction except that it clears the interrupt routine flip-flop. The "end interrupt" instruction will cause a return to the main program at the point where it was interrupted. Only a priority external device may interrupt an "interrupt sub-routine." When automatic interrupts are not available, the programmer must write a scanning program that

repeatedly checks certain conditions to see whether the main program should be interrupted. The ability to use the trapped interrupt feature to handle such conditions as arithmetic overflow gives the programmer the opportunity to make any necessary corrections and reenter the main program to continue the calculations. By being able to selectively arm and disarm traps, the programmer has complete program control over either initiating an interrupt when a particular condition occurs or ignoring its occurrence.

The following is a description of the interrupt conditions:

BUSY interrupt will occur if an external device is instructed to do something which it cannot do because either the device or its assembly register is busy. This interrupt may also occur if an "assembly register" instruction addresses a busy channel.

#### External Device Interrupt

External device interrupt will occur when an ED sends a signal to the central computer that it desires to transmit information. External device interrupt addresses are assigned octal numbers from 00000-00077. These numbers are scanned through periodically to see if an ED requests interrupt. The normal ED's are assigned interrupt addresses at the low end of the memory (i.e., 00,02,04,06, ...) corresponding to the ED addresses. When an ED requests interrupt, the ED interrupt flip-flop is set, the current instruction is completed and the address of the next instruction, is stored in a fixed location 00110. Then control is transferred (jumped) to the interrupt address corresponding to the ED address which requested the interrupt. An "end interrupt" instruction, which is identical to a jump instruction except that it clears the interrupt sub-routine flip-flop, may be inserted in the interrupt fixed address. Certain ED are assigned priority interrupt addresses in a block at the higher end of the memory (i.e., ...., 66, 68, 70, 72, 74, 76). The lowest number in the block has the highest priority. Only these priority interrupt devices can interrupt a "normal interrupt sub-routine." If a priority ED requests interrupt, the scanner jumps to the priority block and scans through for the highest priority ED requesting interrupt. A second flip-flop is set, the next instruction is stored in fixed location 00114 and control is transferred to priority ED. When the priority interrupt sub-routine is completed and an "end interrupt" jump is executed, the priority interrupt flipflop alone is reset. The normal interrupt

flip-flop is maintained in its set condition. After the interrupt is recognized, the scanner will look for any other priority interrupt. If none is requested, control may be transferred to the original interrupt sub-routine. After this sub-routine is completed and an "end interrupt" jump is executed, the first flip-flop is reset and control may be transferred to the main program.

External devices in which a failure is of critical interest to the running program are assigned a second number (normally the odd address following the proper ED address; i.e., 01,03,05,...). This address is not employed in any ED instruction, but is the address of the fixed memory location associated with a failure interrupt by the particular ED. Thus, there is the possibility of two interrupt routines associated with a particular ED: one for normal interrupt and one for failure.

#### Fault Interrupt

Fault interrupt will occur for the following reason:

Dividend > divisor in "divide"

#### Add Overflow Interrupt

Add overflow interrupt will occur when the result of addition or subtraction exceeds the length of the arithmetic register and changes the sign bit 21.

#### Index Overflow Interrupt

Index overflow interrupt will occur when the result of the augment index instruction exceeds the length of a memory address.

#### Memory Fixed Addresses

| Octal       |                                     |

|-------------|-------------------------------------|

| 00000-00077 | External device interrupts          |

| 00100       | Operator interrupt                  |

| 00101       | Unspecified                         |

| 00102       | Fault interrupt                     |

| 00103       | Add overflow interrupt              |

| 00104       | Exponent overflow interrupt         |

| 00105       | Index everflow interrupt            |

| 00106       | Busy interrupt                      |

| 00107       | Unspecified                         |

| 00110       | Interrupt fixed address             |

| 00114       | Priority ED interrupt fixed address |

| 00115-00117 | Index registers                     |

|             |                                     |

#### Input-Output System-General Features

All transfer of data to or from the computer is conducted via input-output channels which communicate directly with the magnetic core memory of the ASI-210. The access to the memory is time-shared between the operating program and input-output data transfer; in a typical situation, approximately 15 percent of the memory time is available for input-output data transfer. Since the arithmetic and control functions of the operating program do not require access to the memory every computer cycle, they may proceed simultaneously with input-output data transfer with little or no loss in speed.

The standard ASI-210 is provided with one input-output channel. An additional channel may be optionally supplied.

Each piece of on-line peripheral equipment is known as an "External Device" (abbreviated, E.D.). Each external device has an unique address. The ASI-210 can accommodate up to 64 external devices with two-channel operation.

The ASI-210 input-output system is provided with program interrupt features so that testing of the condition of the external devices by the running program is not necessary.

#### MULTIPLE-PROCESSOR G-21-BENDIX COMPUTER DIVISION, LOS ANGELES, CALIFORNIA

Bendix Computer Division is developing a large-scale special purpose computer system with a vast memory and true parallel processing capabilities. The super-system, designated the G-21, will be a multiple-processor computer using proven off-the-shelf components of the G-20 computer system. It will be capable of handling massive amounts of data fed to it from a variety of sources on an on-line, real-time basis.

The system is designed for special military control applications which require the collecting and processing of large amounts of intelligence and operational data for immediate presentation to military commanders.

#### Large Memory

The key to the new G-21 system is the multiple processor design which affords one of the largest memory reservoirs. Up to three

central processor units (CPU's), with 97,344 words of random access common core memory, can be linked in a single system. An additional 8192 words of exclusive memory is reserved for each processor, thereby giving a total high-speed memory capacity of 81,920 words.

Three segments of the same problem or three separate problems may be handled simultaneously with this configuration,

If necessary, several G-21 systems may be interconnected without modification of existing equipment. Transfer of data between systems at extremely high speeds will be possible through completely buffered communication lines under the control of independent input-output processors.

Input to the G-21 in a complex military control center, could come from any number of sources, such as, radar, teletype, microwave, telephone, A/D converters, and analog and digital computers, as well as from conventional computer input units.

#### 24-Hour Problems

Unusual flexibility of the G-21 would allow it to handle so-called "24-hour problems" — continuously receiving data from a number of sources, processing the data, and finally delivering outputs in a variety of forms ranging from luminescent screen display to teletype signal, or even to the firing of a weapon. Design of the system also allows individual problems to be handled without interrupting the 24-hour operation.

A unique self-adapting feature is built into the machine's programming. An executive control program, designed to meet specific user requirements, would recognize the demands being placed on the system, and assign appropriate processors to the same sequence of operations stored in one portion of the common memory, or it can assign one processor to a sequence of operations without affecting the activities of the other processors. It also will switch the role of a processor, at will, among many functions.

#### True Parallel Processing

This flexibility affords true parallel processing, eliminating the need for parts of 2

programming system to operate sequentially. Information can now be traded instantly through use of data tables common to the multiple processors. Through program modules, operating simultaneously, reaction time of one module to conditions as they are identified by another is reduced significantly.

A "fail-safe" feature of the executive program will insure system reliability. If one of the processors should fail, the remaining processors will automatically adjust and hold lower-priority problems until time is available. The most important problems assigned to the machine would be unaffected.

Field tests of G-21 components already in use at G-20 installations indicate assured high-reliability standards for the new machine. As an example, figures gathered from the early months of customer use of the central processors units show an availability record of better than 99 percent.

#### G-21 Programs

Programming packages for the G-21 will include many of the compilers, assemblers, routines, and sub-routines developed over the past 3 years for the G-20.

The G-21 is the second phase in the development of a universal computer design aimed at eliminating the obsolescence problem for computer users. Future Bendix computer developments will be keyed to G-20 and G-21 concepts, to provide compatibility with existing systems.

Standard hardware elements, in addition to the central processors, include high-speed magnetic tape units, high-speed printers, disc memory units, auxiliary core memory units, control buffers, data communicators, and punched-card and punched-paper tape units.

Price of the system will vary according to application needs, but a minimum G-21 system (two CPU's, one data communicator, three memory units, one high-speed line printer, three magnetic tape units) will cost upwards of \$1,250,000. Approximate delivery date will be 18 months from receipt of order.

CONTROL DATA 3600— CONTROL DATA CORPORATION, MINNEAPOLIS 20, MINNESOTA

Control Data Corporation recently released details on their new, powerful, large-scale digital computer – Control Data 3600. This computer features modular expandability of its high-speed magnetic core memory, high-speed data communication channels, and computing power. Control Data Corporation takes pride in making this announcement less than 2-1/2 years after delivery of their first large-scale computer – the highly successful 1604. The first 3600, with a complete programming system included, is scheduled to be ready for delivery in approximately 1 year.

The system is exceptionally suited for handling large-volume data processing and solving large-scale scientific problems at very high speeds. The advanced level of speed and flexibility in the 3600 are especially important in real-time applications where computed results must be available nearly as fast as the problem is presented to the computer. The special features in the 3600 offer superior inherent machine capabilities at a price substantially less than other computers approaching the capabilities of the 3600. One of these advanced capabilities is the modular design of the 3600 which permits smooth expansion of a basic 3600 system in step with the user's increased requirements as they arise. This is achieved without the necessity of inter-connecting the modules with control units, or "black boxes."

The magnetic core memory of the 3600, expandable in modules from 1-1/2 million bits of information to more than 12-1/2 million bits, has an information access time of less than 1 microsecond. The 3600 utilizes special circuits, which make use of tunnel diodes, to speed up basic arithmetic processes in the nanosecond for billionths of a second range.

In transmitting data to and from peripheral equipment, the data communication module

operates independently and asynchronously of the main computer program. Each data communication module has four bi-directional data channels, expandable to eight at the customer's option. These high-speed channels permit data to be transmitted to and accepted from peripheral equipment in large-volume and at tremendously high speeds while the computer continues to perform highly complex computations. As many as 32 bi-directional data channels can be incorporated in the fully expanded 3600, each able to handle up to eight control and/or peripheral devices.

A complete programming system will be delivered with the first 3600 computer system. Oriented around the Control Data Master Control System (MCS), the computer programming will be totally independent of the hardwaresize and type of a given 3600 system, whether the customer has a basic or an expanded version. Therefore, the programming will be as tailor-made to the customer's requirements as is the hardware used. The MCS provides for a common library to incorporate systems programming such as FORTRAN and COBOL, an open-ended feature to incorporate new compilers and programming systems as they are developed, and a "linking-loader" feature to incorporate several independently compiled or assembled sub-programs into one main computer program.

A basic 3600 computer system, including necessary peripheral equipment, is in a purchase price range of \$2 to \$2-1/2 million.

Lease of the same equipment will be approximately \$55,000 to \$60,000 per month. This price includes, as standard 3600 computer hardware, many features that are generally held as optional in other systems approaching the capabilities of the 3600. For example, both fixed- and floating-point arithmetic, in both single and double precision, is standard in all 3600 systems.

#### Characteristics

#### Modular Design and Expandability

| Basic System                                                     | Expandable to                                                                                                                        |

|------------------------------------------------------------------|--------------------------------------------------------------------------------------------------------------------------------------|

| 3604 Compute Module                                              | As many as five compute modules can be linked together.                                                                              |

| 3603 Storage Module                                              |                                                                                                                                      |

| 32,768 48-bit words in each module, each word with 3 parity bits | Expandable in 32,768-word modules to a total of eight for more than 12-1/2 million bits of information.                              |

| 3602 Communication Module                                        |                                                                                                                                      |

| Equipped with four (4) high-speed 3606<br>Data Channels          | Expandable up to eight data channels per<br>module, up to eight modules per 3600 com-<br>puter. Total expansion to 32 bi-directional |

| 3601 Console                                                     | channels. (As many as eight control and/or                                                                                           |

| Includes input-output electric typewriter                        | peripheral devices can be handled by each bi-directional data channel.)                                                              |

| 250-card-per-minute punched card reader                          |                                                                                                                                      |

#### Operating Speeds

#### Magnetic Core Memory

| Memory cycle time             | 1.5 | microseconds |

|-------------------------------|-----|--------------|

| Effective cycle time (access) | 0.7 | microseconds |

#### Internal Computing Speeds

Typical average execution times are given in microseconds.

| Instructions | Fixed Point | Single Precision<br>Floating Point | Double Precision<br>Floating Point |  |

|--------------|-------------|------------------------------------|------------------------------------|--|

| Multiply     | 1-6         | 1-6                                | 2-26                               |  |

| Divide       | 1-14        | 1-14                               | 2-26                               |  |

| Fetch/Store  | 1.5-2.2     | 1.5-2.2                            | 3                                  |  |

| Add/Subtract | 1.5-2.2     | 4                                  | 5                                  |  |

### Special High-Speed Circuits

These special circuits employ tunnel diodes to speed up basic arithmetic operations into the nanosecond range. These operate at 4 nanoseconds per stage.

The basic cycle time of the adder network, for example, is 250 nanoseconds. The shift time is a constant 250 nanoseconds regardless of the number of places shifted.

#### Examples of Arithmetic Function Speeds

The 3600 Computer can perform the following functions in 1 second:

670,000 fixed-point additions or subtractions

250,000 floating-point additions or subtractions in single precision

200,000 floating-point additions or subtractions in double precision

- 167,000 floating-point multiplications (single precision)

- 71,500 floating-point divisions (double precision)

- 38,500 floating-point multiplications and/or divisions in double precision

#### Input-Output Communications

Input an i output operations occur independently and asynchronously with operations in the compute module. The standard four bi-directional data channels in each communication module (or expanded modules with eight channels) permit data to be transmitted to and accepted from peripheral equipment in large volume and at tremendously high speeds while the computer continues to perform highly complex computations. The computer only directs the selection of a specific external device and the channel in which the I/O activity is to take place. Once operating conditions have been initiated, the communication module supervises all I/O functions. Data being transmitted or received goes to or from the magnetic core memory directly, and does not pass through the compute module.

#### Computation Capabilities

The 3604 compute module performs all computing and logical operations in the 3600 system. Included as standard hardware in the compute module are provisions for fixed- and floating-point arithmetic in both single and double precision. The 3604 operates in a parallel binary mode.

Several new categories of instructions have been included in the 3600 instruction repertoire:

- 1. Commands for manipulating portions, or "bytes," of a data word. For example, bytes of 48 bits or less may be transmitted to any portion of a computer register or memory storage word in a single operation. Indexing through bytes in a word (horizontally) or through a list of such words (vertically) in the same operation is also provided.

- 2. Double-precision, floating-point commands include add, subtract, multiply, divide, fetch, and store. (A 10-bit plus sign exponent is used with an 84-bit plus sign fraction.)

- 3. A special instruction for list processing, as well as several new indexing operations.

- 4. A universal bit-sensing instruction that permits any bit to be tested and branched upon.

- 5. A powerful, extremely fast, interrupt facility is provided, as well as instructions for processing interrupts.

- 6. Six sense switches are included on the console and can be programmed sensed. These are in addition to three selective jump and three selective stop switches.

- 7. A 48-bit sense-light register able to set or clear each position in a register under program or manual control.

- 8. Two bounds registers of 18 bits each, used for memory lockout. Information is not written into the region of the memory specified by the addresses within the bounds registers.

Other important features in the 3600 are:

- 1. Two-way search instructions

- 2. Auto-load buttons for card and magnetic tape equipment

- 3. Direct card reader entry into arithmetic register

- 4. Parity check on all I/O data transmission

- 5. Special computing functions can be added easily via special channel in the compute module (i.e., trigonometric and exponential functions, etc.).

#### Programming

In parallel with the development of the 3600, Control Data is developing a complete and integrated software system to be delivered with the first computer. This software system will be oriented around a Master Control System (MCS).

The MCS will act as a common communication link among all programming systems and I/O devices, interrupt, and memory allocation functions. Thus, the MCS will allow programming systems to be independent of particular machine configurations, as well as of types and numbers of I/O media. In addition, the MCS will provide:

- A library common to all systems, such as FORTRAN and COBOL, which will operate within the MCS.

- An open-ended ability to incorporate new compilers and operating systems as they are developed.

- 3. A linking loader that will permit joining together, in one program, several sub-programs that may have been separately and independently compiled or assembled.

- A system easy to modify and adapt, when necessary, to the needs peculiar to a given installation.

Some of the important programming systems operating under control of the MCS will be:

MONITOR SYSTEM. A complete operations supervisory system for automatic control of all jobs. It will allow stacking of jobs with arbitrary intermixing of different job types, such as assembly, compilation, and execution.

COMPASS. A comprehensive assembly system with versatile language features for representing the extensive instruction repertoire in a simple symbolic notation, employing advanced assembly techniques.

FORTRAN. An algebraic compiler with extensions to, and generalizations of, the basic FORTRAN language using advanced compiler techniques for producing optimum object programs.

COBOL. A complete compiling system for business-oriented applications.

1604 Compatibility Package. A software package which will execute interpretively all trapped I/O instructions of a 1604 program running in the 1604 compatibility mode.

#### Optional Peripheral Items

A variety of optional on/off-line peripheral items may be used with the 3600 computer. These include 12-, 24-, and 48-bit bi-directional data channels; a 48-bit inter-computer data channel; special function generators; magnetic tape handlers and tape synchronizers; mediumand high-speed card readers, card punches; low- and high-speed line printers; paper tape I/O equipment; keyboard entry devices and typewriters; and disc files.

CONTROL DATA 6600 CONTROL DATA CORPORATION,

MINNEAPOLIS 20, MINNESOTA

Control Data Corporation has announced that the Company has received from the U.S. Atomic Energy Commission a \$5,574,000 order to furnish and install a super, high-speed computer system at the Lawrence Radiation Laboratory. The system, called the Control Data 6600, is to be installed and ready for acceptance testing at the Livermore (California) laboratory not later than February 29, 1964. The Lawrence Radiation Laboratory is operated for AEC by the University of California.

Control Data Corporation was selected to furnish the new system on the basis of its proposal made in response to a solicitation to the computer industry by AEC in 1961, with the delivery of the system requested in mid-1963. Under the terms of the negotiated contract, the Company will furnish interim computer capacity on the Control Data 3600 Computer System (see 3600 description, this issue of DCN) until the new system is accepted. The request for proposals stipulated that the system required, although faster than any existing machine, was not to be a specially designed

computer. It was to be capable of high speed operation for employment in the solution of broad complex scientific problems.

The Control Data 6600 Computer System includes a single central processor with a high-speed arithmetic and logical unit, a central memory of 61,440 words, peripheral processors, associated consoles, and input-output equipment. The system central processor is a high-speed, logical and arithmetic unit, especially designed for rapid floating-point operations.

The high speed in computing is obtained through the use of semi-micro instructions and multiple transistor registers for temporary storage. Simple instructions can be combined optimally to execute complicated sequences without loss of time in referencing core storage temporary locations.

The new computer system will enable scientists to cope with the increasingly complex problems that scientific advances pose and to obtain solutions to present problems in finer overall detail. The new system, which was designed to be faster than any now existing, will make it possible to solve in shorter time comprehensive technical problems that now require many hours of machine operation. Thus, the addition of CONTROL DATA 6600 will significantly increase the overall work capacity of the Lawrence Radiation Laboratory.

HYDAC SERIES 2000—HYBRID DIGITAL/ ANALOG COMPUTER, ELECTRONIC ASSOCIATES, INC., LONG BRANCH, NEW JERSEY

The EAI HYDAC Series 2000 Hybrid Digital/Analog Computer introduces a new concept to engineering and scientific computation by providing the engineer with a single computer that he can easily operate alone and apply either analog or digital techniques as desired to the solution of the problem. The costly process previously practiced in attempts at hybrid computation - that of combining a complete digital data processing computer with an analog computer - has been refined considerably and made economically practical. Analog and digital operations are now combined in one centralized system to achieve a computational efficiency that is well beyond the limits of either analog or digital computers used alone. The traditional advantages of both analog and digital computers - the analog computer's speed, lower cost, and ease of programming and the digital computer's unique capacity for data storage

and time sharing of components – have been combined to expand problem solving capabilities at lower cost.

Since many of the digital operations required for hybrid computation schemes involve mainly those of timing, selection, sequencing, memory look-up, and calculation of simple functions, such schemes can be accomplished without the expense of large data processing digital machines. Digital operations can become an integral part of the expanded general purpose analog computer making them available to computer laboratories that have no digital computers, or during those periods when time is not available on the latter. With HYDAC Series 2000, analog and digital computation can be centralized in a single laboratory thereby eliminating scheduling and training difficulties.

Programming of the entire system parallels closely the relatively simple operation of the analog computer. The transition from the use of relays and switches in the general purpose analog computer to logic devices is made very easy. Extensive retraining of analog programmers is unnecessary.

Analog operations of summation, inversion, continuous integration, multiplication, division, and function generation are performed by a proven computing system. All electronic, wide bandwidth computing components insure high dynamic accuracy for real-time or repetitive mode of operation. Multiplication and other nonlinear operations are performed with signal frequencies in the kilocycle range, so as to realize full advantage of the high-speed digital circuits.

#### Digital Computing Components

Digital computing components are general purpose in concept and design. Five major groups of components are available to provide programmed digital logic, digital memory, analog memory, analog digital conversion, and advanced digital arithmetic. Each of these groups of components could be the complete justification for HYDAC Series 2000, however, a more powerful and useful system is one that combines several of the major classes of digital components.

Modular designed digital building blocks permit fullest advantage of the economy and flexibility of the pre-patch panel concept to be realized. Digital switching circuits employing one basic type of universal gating circuit for maximum flexibility and added economy are

used to perform basic digital operations. Completely solid state with 20-megacycle switching capabilities these basic modules are combined on printed circuit cards to form more complex operations.

The 2000 is the result of a comprehensive design study by experienced computer users, programmers, and designers who are concerned with the basic requirements of hybrid computation.

Major components of the 2000 are a general purpose analog computer and a digital console. This console is designed to take fullest advantage of the economy and flexibility of the pre-patch panel concept; modularized digital building blocks capable of performing basic digital operations plug into standard connectors behind the patch panel, and each is terminated in a four-byten hole area of the patch panel. The digital building blocks are interchangeable. HYDAC Series 2000 may be made to have many different capabilities by employing different combinations of building blocks. This flexibility is obtainable without prejudice to design or wiring of the digital console. Reliability, economy, and ease of maintenance result from all solid-state design.

Digital operations in the 2000 are assembled from the following console units and groups of digital computing components.

#### Digital Console

With provisions for mounting the digital computing components, the basic console unit provides power supplies with necessary wiring, facilities for control and slaving of the unit to the analog computer, selector switches, flipflop indicator lights, and control buttons, etc., and the 3450-hole pre-patch panel system. A clock unit with timing signals terminated on the patch panel provides control timing and syncuronization for the entire system. Console expansion units available include a punched-papertape input-output system, a decimal-binary conversion system and special control units.

#### Logic Building Blocks

Logic components are very high speed (50 nanoseconds switching time), solid-state switching circuits, each designed to provide specific logic functions. A wide choice of functions is available, as well as a choice of the level of logical organization, such as: logic gates, RST flip-flops, 4-bit shift registers, monostable multivibrators, up-down counters, preset

counters, ring counters, BCD counters, differentiators, buffer registers, adders, multipliers, special control units, and timing units.

#### Digital Memory Building Blocks

High-speed digital memory units, known as serial memory units, are available in four different sizes with circuits to make it possible to provide control directly from the patch panel and to connect the units together for special functions.

#### Analog/Digital Converters

These building blocks convert control signals and analog voltage signals from analog to digital, and back to analog. High-speed electronic switches and incremental converters, as well as conventional whole number converters, are also available to satisfy additional conversion requirements.

#### Analog Switching and Memory

These building blocks consist of MICRO-STORE memory and switching modules which are operated in combination with analog operational amplifiers to provide high-speed point storage of analog voltages plus electronic switching capabilities.

#### Advanced Digital Arithmetic Units

These digital building blocks consist of accumulators, adders, summers, input units, constant storage units, and comparators. These units provide the analog computer with expansion units capable of high precision computations.

#### Applications

The combination of analog and digital operations not only allows more economic analysis of certain classes of engineering and scientific problems, but in some instances is a far superior method of analysis. Although the range of applications of the analog computer is indeed wide, the additional ability to store, to process data, and to use the results of this processing as input data for further calculations extends the scope of application of the analog machine. HYDAC Series 2000 provides these capabilities and thus increases the range of problems that the analog computer can

solve economically. It gives new meaning to high-speed computation.

Among the more important applications of this new computer are:

#### Iteration and Optimization Studies

Problems of this nature arising in model building, process simulation, parameter studies, and end-point boundary value systems can be optimized by trial and error methods. Computation time is significantly reduced by the incorporation of suitable logic and switching functions to allow the analog computer to proceed automatically through a complete iteration procedure until an optimum is found. The same logic functions facilitate the automatic programming of parameter searches, performance curve fitting, and matching of boundary values.

#### Partial Differential Equations

The solution of many scientific problems is represented by the solution of linear or nonlinear partial differential equations. Solutions based on difference techniques utilizing function storage and playback permit equipment savings through the time sharing of analog circuits. Such techniques allow the time-domain simulation of field problems where space variables are replaced by high-speed time sweeping, while the physical analogy of time is preserved. Hybrid operations also facilitate the solution of boundary value partial differential equation problems by the method of characteristics or by integral equation methods through the use of serial solution techniques and time multiplexing.

#### Simulation of Logic Functions

Often a problem being studied is partially represented in its physical description by decision functions. Such problems occur with increasing frequency in the study of space vehicle characteristics and the control of complex processing. A prime example is the simulation of an adaptive control system. Here the dynamic behavior of the system being controlled is represented by normal analog elements while the logic of the control system is represented by the available digital logic elements.

#### Integral Equations

This important class of equations, whether arising directly or indirectly as in the solution of partial differential equations, can be solved efficiently by a combination of analog and digital elements. Simpler investigations, such as those involving the solution of the Volterra and Fredholm integral equations, can be programmed easily using general purpose elements. More complex solutions now become economically all ractive.

おこと はの機器のではなっていまい

#### **Auxiliary Mathematical Functions**

Special operations such as multiplications, transport delay simulation, function generation, slow integration, etc., may be custom designed, with suitable programming, for combined operations with analog elements.

Problems which have been programmed for solution with the 2000 at EAI's Princeton Computation Center include:

- 1. A generalized optimization control program to optimize any non-linear function of  $\underline{n}$  variables that is programmed for an analog computer.

- 2. An eigenvalue problem for determining the normal modes of a vibrating beam.

- A reaction-jet space capsule control problem.

- 4. Iteration solution of tubular reactor and control system design problem.

- 5. Solution of partial differential equations by the method of characteristics.

- 6. Integral equation solution of a boundary value problem.

IBM 7094-INTERNATIONAL BUSINESS MACHINES CORPORATION, WHITE PLAINS, NEW YORK

The IBM 7094 data processing system is the most powerful in the company's line of intermediate- and large-scale solid-state scientific computers. This line also includes the 7040, 7044, and 7090. Increased speed and processing power of the 7094 are provided by faster adding circuitry, additional index registers and instructions, and the facility for performing double-precision floating-point arithmetic.

The new system is offered in a wide variety of input-output configurations and has storage capacity of 32,768 words. It can be linked to various IBM Tele-processing devices for full data transmission ability. A library of 7094 programs covering a wide range of computer functions is provided at no cost by IBM. System compatibility enables a customer with a 7090 to use his new 7094 with virtually no reprogramming.

The memory reference cycle is 2.00 microseconds for the 7094, compared to 2.18 microseconds for the 7090. When processing is performed in the floating-point mode (generally used when the numbers involved vary greatly in magnitude), the 7094 can perform mathematical computations 1.4 to 2.4 times faster than the 7090, depending upon the technique used to solve problems. Memory reference speeds for IBM's intermediate- and large-scale scientific systems are as follows:

| System      | Memory Reference Speed (µsec) |

|-------------|-------------------------------|

| 7094        | 2                             |

| 7090        | 2.18                          |

| 7044        | 2,5                           |

| 7040        | 8                             |

| 709 and 704 | 12                            |

Modular design provides upward compatibility of these systems. A user can enlarge his system or advance to a more powerful computer with a minimum of reprogramming.

A team of IBM customer engineers can expand a 7090 which is already on rental to a 7094 in the user's office within 72 working hours, including installation and system testing. The changeover involves installation of a higher-speed processing unit containing faster solid-state adding circuitry, additional instruction circuitry to accommodate new commands, and four additional index registers. Faster circuitry is installed in other elements of the system and a display panel for the additional index registers is mounted on the operator's console.

Innut-Output

IBM 1301 disk storage units and Hypertape magnetic tape drives can be linked to the system for high-speed input and output of data. Up to five 1301's with a combined capacity of 279 million characters can provide additional storage on magnetic disk files.

Up to 20 Hypertape units, capable of reading data from and writing data on tape at the rate of 170,000 characters a second, or up to 80 IBM 729 tape units, ranging in read-write speed from 41,700 to 90,000 characters a second, can be linked to the system. Various combinations of Hypertape and 729 tape units can be used with a single 7094.

An IBM 1011 paper-tape reader, capable of reading data into the computer at the rate of 500 paper-tape characters a second, enables the system to accept data transmitted directly by teletype. Common carrier telegraph equipment can also serve as remote input-output devices for the system.

Ability to transmit and receive data over long distances in computer language is provided by the IBM 1009 data transmission unit. This IBM Tele-processing device enables the 7094 to communicate over leased telephone or telegraph lines with another computer (7094, 7090, 7040, 7044, 1401, 1410), a magnetic tape transmission unit or a card transmission unit at speeds up to 300 characters per second.

The 1014 remote inquiry unit, another IBM Tele-processing device, is equipped with and input-output typewriter and can be used for direct interrogation of the computer from a point up to 8 miles away.

#### Programming Support

A number of 7090/94 programming systems and languages will be provided by IBM to 7094 users without charge. The 7094 is so designed that programs written for the 704, 709, 7040, 7044, and 7090 can be run with a minimum of modification and at higher speed, 7090/94 programs provided by IBM are:

#### FORTRAN

The widely accepted IBM FORmula TRANslation system enables the user to write his programs in a language closely resembling that of mathematics. Thus scientists and mathematicians can code problems with a

minimum of computer knowledge. The FORTRAN Assembly Program converts these coded instructions into machine language.

#### COBÓL

This <u>COmmon Business Oriented Language</u> permits the user to write programs using familiar business terms. COBOL is the result of work by the Conference on Data Systems Languages (CODASYL), a voluntary effort of various computer manufacturers and users under sponsorship of the Department of Defense. The COBOL processor converts English-like instructions in COBOL language into a machinelanguage program.

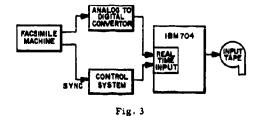

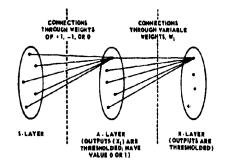

#### Input-Output Control System